## ADC80

## IC ANALOG-TO-DIGITAL CONVERTERS

## **FEATURES**

COMPACT DESIGN - Self-contained with Internal clock, comparator, and reference

32-pin ceramic package

- FAST CONVERSION SPEEDS

Provide fast signal sampling rates

12-bits 25µsec, 10-bits 21µsec

Faster conversion speeds obtainable with

"Short-Cycling" and optional external clock

- LOW COST

- WIDE SUPPLY RANGE Will operate with ±11.4V to ±16V supplies (Z models)

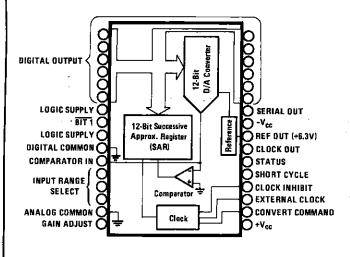

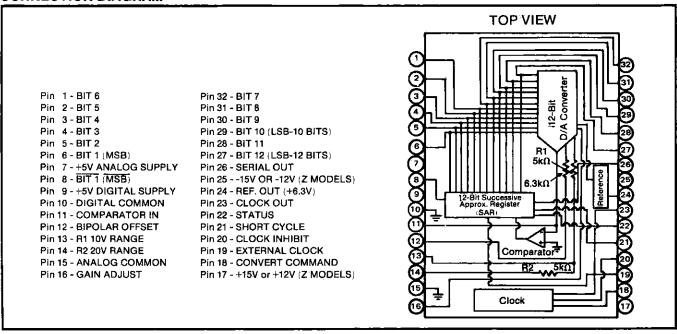

## **FUNCTIONAL DIAGRAM**

## DESCRIPTION

The Model ADC80AG-10 and ADC80AG-12 are 10-and 12-bit successive approximation A/D converters. They utilize state-of-the-art IC and laser-trimmed thin-film components, and are packaged in a compact 32-pin ceramic package.

Complete with internal reference, the ADC80 offers versatility and performance formerly offered only in larger modular or rack-mount packages.

Thin-film internal scaling resistors are provided for the selection of analog input signal ranges of  $\pm 2.5V$ ,  $\pm 5V$ ,  $\pm 10V$ , 0 to  $\pm 5V$  or 0 to  $\pm 10V$ .

Gain and offset errors may be externally trimmed to zero, offering initial accuracies of better than  $\pm 0.0122\%$  ( $\pm 1/2$ LSB). The model ADC80 is specified for -25°C to +85°C operation.

Th fast conversion speeds of  $25\mu$ sec for 12-bit and  $21\mu$ sec for 10-bit resolution make the ADC80 excellent for a wide range of applications where system throughput sampling rates from 40kHz to 47kHz are required. In addition, the ADC80 may be short-cycled and an external clock may be used to obtain faster.

Data is available in parallel and serial form with corresponding clock and status signals. All digital input and output signals are DTL/TTL-compatible. Two power supply ranges are available:  $\pm 15$ V and  $\pm 12$ V (Z models). A+5V logic supply is also required.

## **DISCUSSION OF PERFORMANCE**

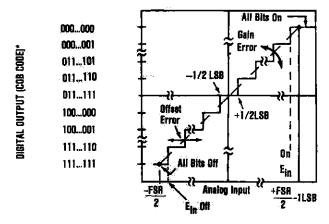

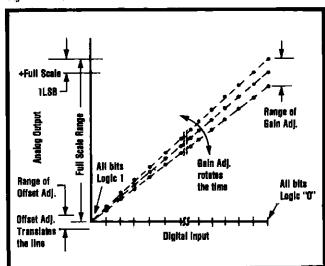

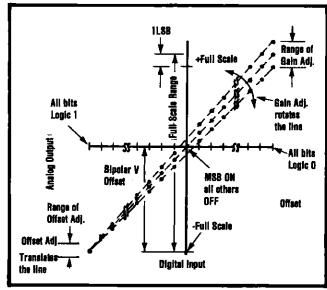

The accuracy of a successive approximation A/D converter is described by the transfer function shown in Figure 1. All successive approximation A/D converters have an inherent Quantization Error of  $\pm 1/2$ LSB. The remaining errors in the A/D converter are combinations of analog errors due to the linear circuitry, matching, and tracking properties of the ladder and scaling networks, power supply rejection, and reference errors. In summary, these errors consist of initial errors including Gain, Offset, Linearity, Differential Linearity and Power Supply Sensitivity. Initial Gain and Offset errors may be adjusted to zero. Gain drift over temperature rotates the line (Figure 1) about the zero or minus full scale point (all bits OFF) and Offset drift shifts the line left or right over the operating temperature range. Linearity error is unadjustable and is the most meaningful indicator of A/D converter accuracy. Linearity error is the deviation of an actual bit transition from the ideal transition value at any level over the range of the A/D converter. A Differential Linearity error of  $\pm 1/2$ LSB means that the width of each bit step over the range of the A/D converter is  $1LSB \pm 1/2LSB$ .

The ADC80 is also Monotonic, assuring that the output digital code either increases or remains the same for increasing analog input signals. A monotonic converter

FIGURE 1. Input vs Output for an Ideal Bipolar A/D Converter.

\*See Table I for digital code definitions..

can have missing codes; therefore, Burr-Brown specifies no missing codes over a temperature range.

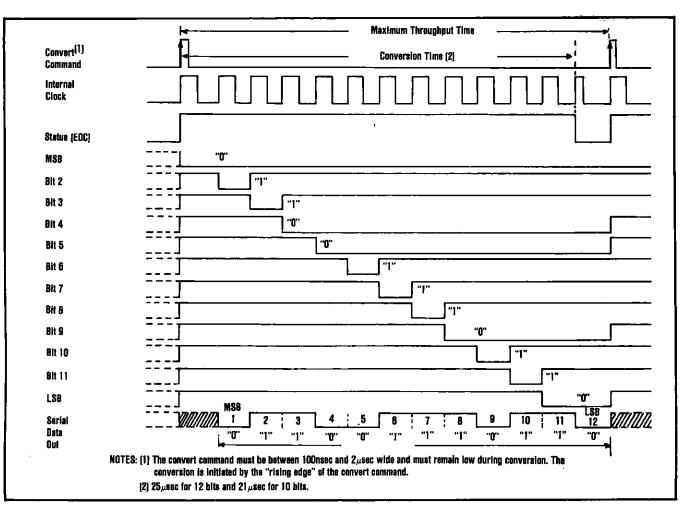

#### TIMING CONSIDERATIONS

The timing diagram of the ADC80 (Figure 2) assumes an analog input such that the positive true digital word 1001-1000 1001 exists. The output will be complementary as shown in Figure 2 (0110 0111 0110) is the digital output.

FIGURE 2. ADC80 Timing Diagram.

## **SPECIFICATIONS**

#### **ELECTRICAL**

Typical at +25°C and rated power supplies unless otherwise noted.

|                                                      |                           | 1                         |               |  |  |

|------------------------------------------------------|---------------------------|---------------------------|---------------|--|--|

| MODEL                                                | ADC80AGZ-12<br>ADC80AG-12 | ADC80AGZ-10<br>ADC80AG-10 | UNITS         |  |  |

| RESOLUTION                                           | 12                        | 10                        | Bits          |  |  |

| INPUT                                                |                           |                           |               |  |  |

| ANALOG INPUTS                                        |                           |                           |               |  |  |

| Voltage Ranges - Bipolar                             | +25 +                     | ±2.5, ±5, ±10             |               |  |  |

| - Unipolar                                           |                           | 0 to +10                  |               |  |  |

| Impedance (Direct Input)                             | 0 10 10,                  | 010110                    | •             |  |  |

| 0 to +5V, ±2.5V                                      | 2.                        | 5                         | kΩ            |  |  |

| 0 to +10V, ±5V                                       | l                         | =                         | kΩ            |  |  |

| ±10V                                                 | 1                         |                           | kΩ            |  |  |

| DIGITAL INPUTS(1)                                    | <del></del>               | ·                         | •             |  |  |

| Convert Command                                      | Positive Pulse 100        | Insec Wide (min)          |               |  |  |

|                                                      | 2µsec Wie                 |                           |               |  |  |

| Logic Loading                                        | 1                         | ·                         | TTL Load      |  |  |

| External Clock                                       | 1                         |                           | TTL Load      |  |  |

| TRANSFER CHARACTERISTICS                             | ·                         | <del></del>               |               |  |  |

| ERROR                                                |                           |                           |               |  |  |

| Gain Error(2)                                        | <u>+</u> 0                | 1                         | %             |  |  |

| Offset Error(2) - Unipolar                           | ±0.                       |                           | % of FSR(3)   |  |  |

| - Bipolar                                            | +0                        |                           | % of FSR      |  |  |

| Linearity Error, max(4)                              | ±0.012                    | • •                       | % of FSR      |  |  |

| Inherent Quantization Error                          | ±1                        |                           | LSB           |  |  |

| Differential Linearity Error                         | ±1                        |                           | LSB           |  |  |

| No Missing Codes Temp. Range                         | 0 to +70                  |                           | °C            |  |  |

| Power Supply Sensitivity                             |                           |                           | 1             |  |  |

| ±15V                                                 | ±0.0                      | 030                       | % of FSR/%VS  |  |  |

| +5V                                                  | ±0.0                      | % of FSR/%VS              |               |  |  |

| DRIFT                                                |                           |                           |               |  |  |

| Specification Temperature Range                      | -25 to                    | +85                       | °C            |  |  |

| Total Accuracy, Bipolar, max(5)                      | ±2                        | :3                        | ppm/°C        |  |  |

| Gain, max                                            | ±3                        | =                         | ppm/°C        |  |  |

| Offset - Unipolar                                    | ±                         |                           | ppm of FSR/°C |  |  |

| Bipolar, max                                         | ±1                        |                           | ppm of FSR/°C |  |  |

| Linearity, max                                       | ±                         |                           | ppm of FSR/°C |  |  |

| Monotonicity                                         | GUARA                     | NTEED                     |               |  |  |

| CONVERSION SPEED (max)(6)                            | 25                        | 22                        | μsec          |  |  |

| ОUТРUТ                                               |                           |                           |               |  |  |

| DIGITAL DATA                                         |                           |                           |               |  |  |

| (all codes complementary)                            |                           |                           |               |  |  |

| Parallel                                             |                           |                           | i I           |  |  |

| Output Codes(7) - Unipolar                           | CS                        | 8                         | į <b>I</b>    |  |  |

| - Bipolar                                            | сов,                      |                           | 1             |  |  |

| Output Drive                                         | 2                         |                           | TTL Loads     |  |  |

| Serial Data Codes (NRZ)                              | CSB,                      |                           |               |  |  |

| Output Drive                                         | 2                         |                           | TTL Loads     |  |  |

| Status                                               | Logic "1" duri            |                           | <u> </u>      |  |  |

| Status Output Drive                                  | 2                         |                           | TTL Loads     |  |  |

| Internal Clock                                       | _                         |                           |               |  |  |

| Clock Output Drive                                   | 2                         |                           | TTL Loads     |  |  |

| Frequency(8)                                         | 50                        | <u> </u>                  | kHz           |  |  |

| INTERNAL REF. VOLTAGE Max. External Current (with no | 6.                        |                           | V             |  |  |

| degradation of specifications)                       | 20                        |                           | μΑ            |  |  |

| Tempco of Drift, max                                 | <u>+2</u>                 | 0                         | ppm/°C        |  |  |

| POWER REQUIREMENTS                                   |                           |                           |               |  |  |

| Rated Voltages                                       | ±15,                      | +5                        | V             |  |  |

| Z models                                             | ±12,                      |                           | v             |  |  |

| Range for Rated Accuracy                             | 4.75 to 5.25 and          |                           | V             |  |  |

| Z models                                             | 4.75 to 5.25 and          |                           | v .           |  |  |

| Supply Drain +15V or +12V                            | +2                        | :='                       | mA            |  |  |

| -15V or -12V                                         | -2                        | =                         | mA            |  |  |

| +5V                                                  | +7                        | <u>U</u>                  | m <b>A</b>    |  |  |

| TEMPERATURE RANGE                                    |                           |                           |               |  |  |

| Specification                                        | -25 to                    | +85                       | °C            |  |  |

| Operating (derated spec)                             | -55 to                    | +100                      | °C            |  |  |

| Storage                                              | -55 to                    | +125                      | °C            |  |  |

|                                                      |                           |                           |               |  |  |

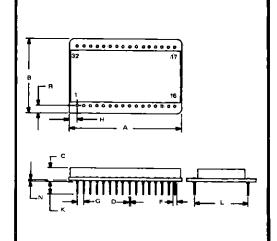

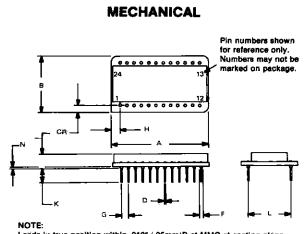

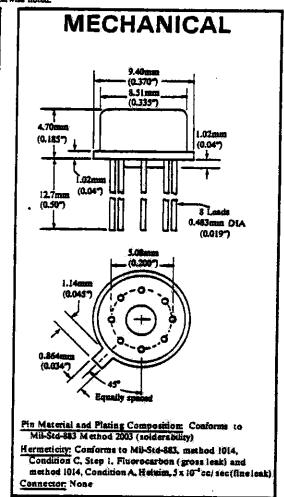

## **MECHANICAL**

NOTE: LEADS IN TRUE POSITION WITHIN .010" (.25mm) R. @ MMC AT SEATING PLANE.

| 1   | INC     | HES   | MILLIN  | METERS |

|-----|---------|-------|---------|--------|

| DIM | MIN     | MAX   | MIN     | MAX    |

| Α   | 1.700   | 1.760 | 43.18   | 44.70  |

|     | 1.120   | 1.160 | 28.45   | 29,46  |

| С   | .170    | .230  | 4.32    | 5.84   |

| ٥   | .018    | .021  | 0.46    | 0.53   |

| F   | .035    | .050  | 0.89    | 1.27   |

| Ģ   | .100 B  | ASIC  | 2.54 8  | ASIC   |

| н   | .110    | 130   | 2.79    | 3.30   |

| К   | 150     | .250  | 3.81    | 6.35   |

| L   | 900 B   | \sic  | 22.86 B | ASIC   |

| N   | .002    | .010  | 0.05    | 0.25   |

| A   | 110 130 |       | 2.79    | 3.30   |

CASE: Ceramic

MATING CONNECTOR: 2302MC - Set of

two 16-pin strips \$9.40 per set.

WEIGHT: 13 grams (0.46oz.)

- 1. DTL/TTL compatible, i.e., Logic "0" = 0.8V max, Logic "1" = 2.0V min for inputs and for digital outputs, Logic "0" = +0.4V max and "1" = 2.4V min.

- 2. Adjustable to zero with external trimpots.

- FSR means Full Scale Range for example, unit connected for ±10V range has 20V FSR.

- Error shown is the same as ±1/2LSB max for resolution of A/D converter.

- 5. Includes drift due to linearity, gain, and offset drifts.

- 6. Conversion time with internal clock.

- 7. See Table I. CSB Complementary Straight Binary.

COB Complementary Offset Binary.

- CTC Complementary Two's Complement.

- 8. For conversion speeds specified.

#### CONNECTION DIAGRAM

## TYPICAL PERFORMANCE CURVES

## **DEFINITION OF DIGITAL CODES**

#### PARALLEL DATA

Three binary codes are available on the ADC80 parallel output; they are complementary (logic "0" is true) straight binary (CSB) for unipolar input signal ranges and complementary two's complement (CTC) and complementary offset binary (COB) for bipolar input signal ranges.

Table I describes the LSB, transition values and code definitions for each possible ADC80 analog input signal

### **SERIAL DATA**

Two straight binary (complementary) codes are available on the serial output line of the ADC80; they are CSB and COB. The serial data is available only during conversion and appears with the most significant bit (MSB) occurring first. The serial data is synchronous with the internal clock as shown in the timing diagram of Figure 2. The LSB and transition values shown in Table I also apply to the serial data output except for the CTC code.

TABLE I. Input Voltages, Transition Values, LSB Values, and Code Definitions.

| Binary (BIN) Output                   | · <u> </u>                            | INPUT VOLTAGE RANGE AND LSB VALUES |                                  |                                        |                                  |                                        |  |  |  |  |

|---------------------------------------|---------------------------------------|------------------------------------|----------------------------------|----------------------------------------|----------------------------------|----------------------------------------|--|--|--|--|

| Analog Input<br>Voltage Range         | Defined As:                           | ±10V                               | +5V                              | ±2.5∨                                  | 0 to +10V                        | 0 to +5V                               |  |  |  |  |

| Code<br>Designation                   |                                       | COB<br>or CTC*                     | COB<br>or CTC*                   | COB<br>or CTC*                         | CSB **                           | CSB **                                 |  |  |  |  |

| One Least<br>Significant<br>Bit (LSB) | <u>FSR</u><br>2 <sup>n</sup><br>n = 8 | 20V<br>2 <sup>n</sup><br>78.13mV   | 10V<br>2 <sup>n</sup><br>39.06mV | <u>5V</u><br>2 <sup>n</sup><br>19.53mV | 10V<br>2 <sup>n</sup><br>39.06mV | <u>5V</u><br>2 <sup>n</sup><br>19,53mV |  |  |  |  |

|                                       | n = 10<br>n = 12                      | 19.53mV<br>4.88mV                  | 9.77mV<br>2.44mV                 | 4.88mV<br>1.22mV                       | 9,77mV<br>2,44mV                 | 4,88mV<br>1,22mV                       |  |  |  |  |

| Transition Values MSB LSB             |                                       |                                    |                                  |                                        |                                  |                                        |  |  |  |  |

| 000, 000 ***<br>011, 111              | +Full Scale<br>•Mid Scale             | +10V-3/2LSB                        | +5V -3/2LSB<br>0                 | +2.5V -3/2LSB                          | +10V -3/2LSB<br>+5V              | +5V -3/2LSE<br>+2.5V                   |  |  |  |  |

| 111 110                               | -Full Scale                           | ~10V +%LSB                         | -5V +%LSB                        | -2.5V +%L\$B                           | 0 + %LSB                         | 0 + 1/4 LSB                            |  |  |  |  |

CSB = Complementary Straight

available on pin 8.

## DISCUSSION OF SPECIFICATIONS

The ADC80 is specified to provide critical performance criteria for a wide variety of applications. The most critical specifications for an A/D converter are linearity, drift, gain and offset errors and conversion speed effects on accuracy. The ADC80 is factory-trimmed and tested for all critical key specifications.

#### GAIN AND OFFSET ERROR

Initial Gain and Offset errors are factory-trimmed to ±0.1% of FSR (±0.05% for unipolar offset) at 25°C. These errors may be trimmed to zero by connecting external trim potentiometers as shown on next page.

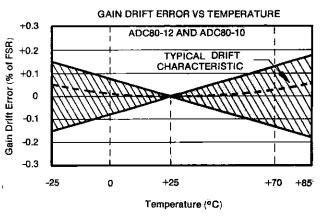

## **ACCURACY DRIFT VS TEMPERATURE**

Three major drift parameters degrade A/D converter accuracy over temperature; they are gain, offset and linearity drift. The worst case accuracy drift is the summation of all three drift errors over temperature. Statistically, these errors do not add algebraically, but are random variables which behave as root-sum-squared (RSS) or 1δ errors as follows:

RSS =

$$\sqrt{\epsilon g^2 + \epsilon o^2 + \epsilon e^2}$$

where  $\epsilon g$  = gain drift error (ppm/°C)

$\epsilon o$  = offset drift error (ppm of FSR/°C)

$\epsilon e = linearity error (ppm of FSR/°C)$

For unipolar operation, the total RSS drift is  $\pm 30.3$ ppm/°C.

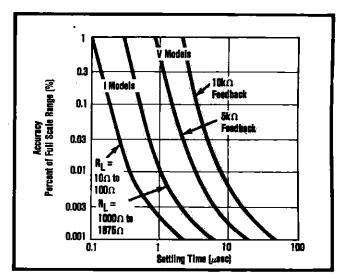

#### **ACCURACY VS SPEED**

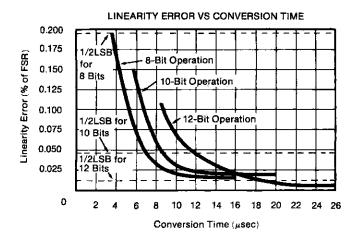

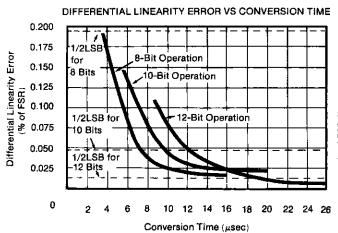

In successive approximation A/D converters, the conversion speed affects linearity and differential linearity errors. Conversion speed and its effect on linearity and differential linearity errors for the ADC80 are shown in Typical Performance Curves.

The ADC80 conversion speeds are specified for a maximum linearity error of  $\pm 1/2LSB$  and a differential linearity error of ±1/2LSB with the internal clock. Faster conversion speeds up to 23µsec for 12 bits, 12µsec for 10 bits and 6µsec for 8 bits are possible with an external clock.

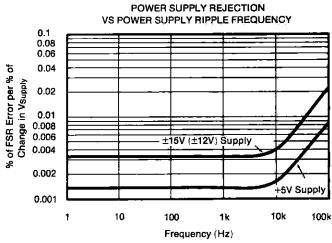

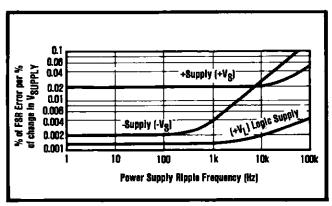

#### **POWER SUPPLY SENSITIVITY**

Changes in the DC power supplies will affect the accuracy of the ADC80. The ADC80 power supply sensitivity is specified for  $\pm 0.003\%$  of FSR/%Vs for  $\pm 15V$  ( $\pm 12V$ ) supplied for  $\pm 0.0015\%$  of FSR/%Vs for  $\pm 5V$  supplies. Normally, regulated power supplies with 1% or less ripple are recommended for use with the ADC80. See layout precautions and power supply decoupling on next page.

complement of the most significant bit (MSB). MSB is

nominal value for transition to the code specified.

## LAYOUT AND OPERATING INSTRUCTIONS

#### LAYOUT PRECAUTIONS

Analog and digital commons are not connected internally in the ADC80 but should be connected together as close to the unit as possible, preferably to a large ground plane under the ADC80. If these grounds must be run separately, use wide conductor pattern and a  $0.01\mu$ F to  $0.1\mu$ F nonpolarized bypass capacitor between analog and digital commons at the unit. Low impedance analog and digital common returns are essential for low noise performance. Coupling between analog input and digital lines should be minimized by careful layout. Analog and digital +5V supplies are also not connected internally; they should be connected together at the unit as shown below in Figure 3 (Pins 7 and 9).

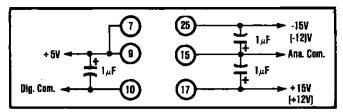

#### **POWER SUPPLY DECOUPLING**

The power supplies should be bypassed with tantalum or electrolytic type capacitors as shown in Figure 3 to obtain noise free operation. These capacitors should be located close to the ADC80.  $1\mu$ F electrolytic type capacitors should be bypassed with  $0.01\mu$ F ceramic capacitors for improved high frequency performance.

FIGURE 3. Recommended Power Supply Decoupling.

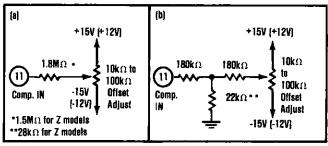

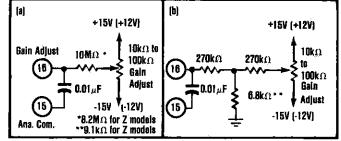

# OPTIONAL EXTERNAL GAIN AND OFFSET ADJUSTMENTS

Gain and Offset errors may be trimmed to zero using external gain and offset trim potentiometers connected to the ADC80 as shown in Figures 5 and 6. Multiturn potentiometers with  $100\text{ppm}/^{\circ}\text{C}$  or better TCR's are recommended for maximum drift over temperature and time. These pots may be any value from  $10\text{k}\Omega$  to  $100\text{k}\Omega$ . All resistors should be 20% carbon or better. Pin 16 (Gain Adjust) may be left open if no external adjustment is required.

### **ADJUSTMENT PROCEDURE**

**OFFSET** - Connect the Offset potentiometer as shown in Figure 5. Sweep the input through the end point transition

FIGURE 5. Two Methods of Connecting Optional Offset Adjust with a 0.4% of FSR Range Adjustment.

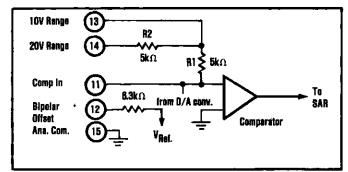

#### **INPUT SCALING**

The ADC80 input should be scaled as close to the maximum input signal range as possible in order to utilize the maximum signal resolution of the A/D converter. Connect the input signal as shown in Table II. See Figure 4 for circuit details.

FIGURE 4. ADC80 Input Scaling Circuit.

TABLE II. ADC80 Input Scaling Connections.

| Input<br>Signal<br>Range | Output<br>Code | Connect<br>Pin 12<br>To Pin | Connect<br>Pin 14<br>To | Connect<br>Input<br>Signal<br>To |

|--------------------------|----------------|-----------------------------|-------------------------|----------------------------------|

| ±10V                     | COB or CTC     | 11                          | Input Signal            | 14                               |

| ±5V                      | COB or CTC     | 11                          | Open                    | 13                               |

| ±2.5V                    | COB or CTC     | 11                          | Pin 11                  | 13                               |

| 0 to +5V                 | CSB            | 15                          | Pin 11                  | 13                               |

| 0 to +10V                | CSB            | 15                          | Open                    | 13                               |

voltage that should cause an output transition to all ones.

Adjust the Offset potentiometer until the actual end point transition voltage occurs at  $E_{IN}^{OFF}$ . The ideal transition voltage values of the input are given in Table I.

**GAIN** - Connect the Gain adjust potentiometer as shown in Figure 6. Sweep the input through the end point transition voltage that should cause an output transition to all zeros.

Adjust the Gain potentiometer until the actual end point transition voltage occurs at  $E_{IN}^{ON}$ .

Table I details the transition voltage levels required.

FIGURE 6. Two Methods of Connecting Optional Gain Adjust with a 0.6% Range of Adjustment.

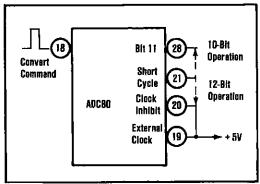

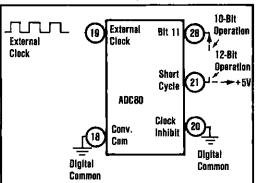

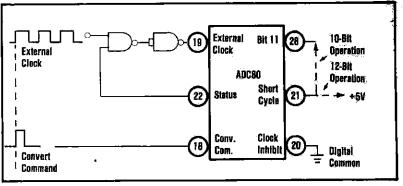

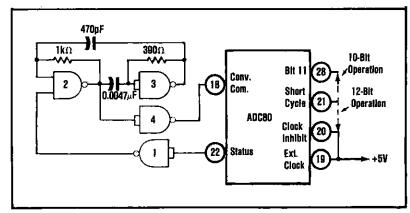

## **CLOCK OPTIONS**

The ADC80 is extremely versatile in that it can be operated in several different modes with either internal or external clock. Most of these options can be implemented

with nothing more than an inexpensive quad 2-input NAND gate (7400) as shown in Figures 7 through 10.

FIGURE 7. Internal Clock - Normal

Operating Mode. (Conversion

initiated by the rising edge of the

convert command. The internal

clock runs only during

conversion.)

FIGURE 8. Continuous Conversion with

External Clock. (Conversion is initiated by 14th clock pulse.

Clock runs continuously.)

FIGURE 9 Continuous External Clock. (Conversion initiated by rising edge of convert command. The convert command must be synchronized with clock.)

FIGURE 10. Continuous Conversion with Internal Clock. (Conversion is initiated by the 14th clock pulse. Clock runs continuously. The oscillator formed by gates 2 and 3 insures that the conversion process will start when logic power is first turned on.)

## SHORT CYCLE FEATURE

The ADC80 may be operated at faster speeds for resolutions less than 10 or 12 bits, depending on the model selected, by connecting the short cycle pin, pin 21, as

shown in Table III. Conversion speeds, linearity, and resolutions are shown for reference.

TABLE III. Short Cycle Connections and Resolutions for 8- to 12-bit Resolutions - ADC80.

| RESOLUTION (BITS) 12                                                               |                      | 10                   | 8       |

|------------------------------------------------------------------------------------|----------------------|----------------------|---------|

| Connect Pin 21 to                                                                  | Pin 9                | Pin 28               | Pin 30  |

| Maximum Conversion Time <sup>(1)</sup> Internal Clock (μsec) External Clock (μsec) | 25<br>23             | 22<br>12             | 18<br>6 |

| Maximum Nonlinearity<br>At +25°C (% of FSR)                                        | 0.012 <sup>(2)</sup> | 0.048 <sup>(3)</sup> | 0.20(3) |

## **OUTPUT DRIVE**

Normally all ADC80 logic outputs will drive 2 standard TTL loads; however, if long digital lines must be driven,

external logic buffers are recommended.

## **APPLICATIONS**

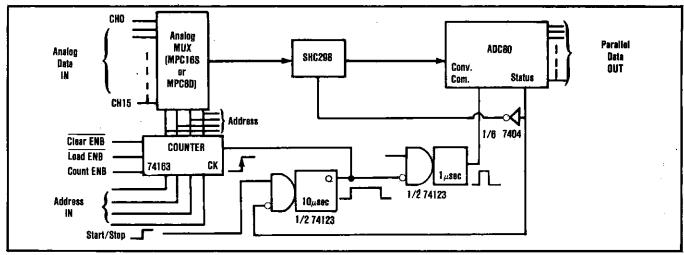

## LOW COST DATA ACQUISITION SYSTEM

When combined with a sample/hold, multiplexer and

simplified logic, a 16-channel 12-bit, 25kHz data acquisition system can be built for less than \$125.00 parts cost.

FIGURE 11. Low Cost Data Acquisition System.

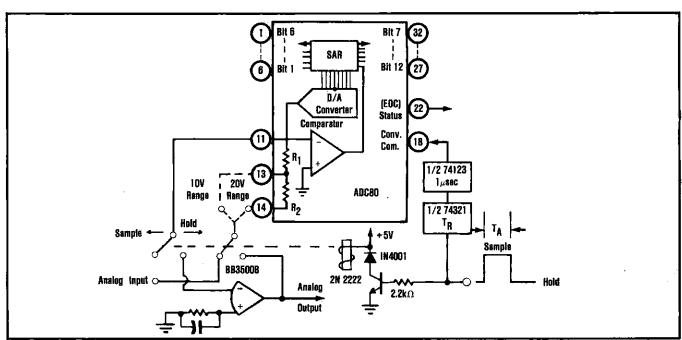

## ZERO DROOP SAMPLE/HOLD

A zero droop - infinite hold sample/hold can be constructed with the ADC80 with the circuit shown in Figure 12. A sample command will cause the relay to switch the analog input to the ADC80 input and also generate a convert command to the ADC80. The sample pulse width (T<sub>A</sub>) should be greater than the combined

switching and settling time of the relay and driver circuit and the ADC80 conversion time.

In the Hold mode, the analog value can be held indefinitely with zero droop. The period of the first one-shot multivibrator must be equal to or greater than  $T_R$ , the switching time of the relay.

FIGURE 12. Zero Droop Infinite Hold Sample/Hold using ADC80 and a Few External Components.

## ORDERING INFORMATION

A/D Converter family A = -25°C to +85°C Z - $\pm$ 11.4V to  $\pm$ 16.0V supply range Resolution (No. of Bits) G = Ceramic Package  $Z - \pm 11.4V = \pm 16.0V = \pm 16.0V = \pm 10.0V = \pm 10.0V$

The information is this publication has been carefully checked and is believed to be reliable; however, no responsibility is assumed for possible inaccuracies or omissions. Prices and specifications are subject to change without notice. No patent rights are granted to any of the circuits herein.

## DAC80

RECEIVED NOV

984

9

# Integrated Circuit DIGITAL-TO-ANALOG CONVERTER

## **FEATURES:**

- WIDE POWER SUPPLY RANGE MODELS AVAILABLE (Z MODELS)

- 12-BIT, 3-DIGIT RESOLUTION

- ±1/2L8B MAXIMUM NONLINEARITY

- COMPLETE WITH INTERNAL REFERENCE AND OUTPUT AMPLIFIER (V MODELS)

- FAST SETTLING 300nsec to ±0.01% (I MODELS)

- CERAMIC DUAL-IN-LINE PACKAGE

- LOW COST

## DESCRIPTION

Use this popular 12-bit digital-to-analog converter for low cost precision performance applications.

DAC80, with internal reference and optional output amplifier, offers a maximum nonlinearity error of ±0.012%, ±30ppm/°C maximum gain drift, and monotonicity - all over a 0°C to 70°C operating range. In the bipolar configuration, total accuracy drift is guaranteed to be less than ±25ppm/°C. Select TTL compatible complementary 12-bit binary (CBI) or 3-digit BCD (CCD) input codes.

Packaged within DAC80's 24-pin dual-in-line ceramic case are fast-settling switches and stable, laser-trimmed thin-film resistors that let you select output voltage ranges of  $\pm 2.5$ ,  $\pm 5$ ,  $\pm 10$ , 0 to  $\pm 5$ , 0 to  $\pm 10$  volts (V models) or output current ranges of  $\pm 1$ mA or 0 to -2mA (I models). Voltage output models settle to  $\pm 0.01\%$  of FSR in  $3\mu$ sec for a 10V step change.

By specifying the new DAC80Z model with a supply range of  $\pm 11.4$ V to  $\pm 16.0$ V, you can use this proven D/A converter in microprocessor and semiconductor memory systems.

## **SPECIFICATIONS**

Typical at 25°C and rated power supplies unless otherwise noted.

| MODEL                                                                                                                                                                                                                   | DAC80CBI                   |                               |                                           | ]                          | DAC80CCD                      |                                           |                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------|-------------------------------------------|----------------------------|-------------------------------|-------------------------------------------|-------------------------------------------------------------|

|                                                                                                                                                                                                                         | MIN                        | TYP                           | MAX                                       | MIN                        | ТҮР                           | MAX                                       | UNITS                                                       |

| DIGITAL INPUT<br>Resolution                                                                                                                                                                                             |                            |                               | 12                                        |                            |                               | 3                                         | Bits<br>Digits                                              |

| Logic Levels (TTL/Compatible)(1)<br>Logic "1" (+40µA max at +5.0V)<br>Logic "0" (1.6mA max at +0.4V)                                                                                                                    | +2.4<br>0                  |                               | +5.0<br>+0.4                              | +2.4<br>0                  |                               | +5.0<br>+0.4                              | VDC<br>VDC                                                  |

| ACCURACY Linearity Error at 25°C Differential Linearity Error Gain Error <sup>(2)</sup> Offset Error <sup>(2)</sup> Monotonicity Temp. Range, min                                                                       | 0                          | ±1/4<br>±1/2<br>±0.1<br>±0.05 | ±1/2<br>+1, -3/4<br>±0.3<br>±0.15<br>+70  | o                          | ±1/8<br>±1/4<br>±0.1<br>±0.05 | ±1/4<br>±1/2<br>±0.3<br>±0.15<br>+70      | LSB<br>LSB<br>%<br>% of FSR(3)                              |

| DRIFT(4) (0°C to +70°C) Total bipolar drift, max (includes gain, offset, and linearity drifts)(5) Total error over 0°C to +70°C(6) Unipolar Bipolar Gain Exclusive of internal reference Unipolar Offset Bipolar Offset |                            | ±0.08<br>±0.06<br>±15         | ±25<br>±0.15<br>±0.12<br>±30<br>±10<br>±3 |                            | ±0.08<br>±0.06<br>±15         | ±25<br>±0.15<br>±0.12<br>±30<br>±10<br>±3 | ppm of FSR/°C % of FSR % of FSR ppm/°C ppm/°C ppm of FSR/°C |

| Bipolar Offset Differential Linearity 0°C to +70°C Linearity Error 0°C to +70°C                                                                                                                                         |                            | ±1/2                          | ±15<br>+1, -7/8<br>±1/2                   |                            | ±1/2                          | ±15<br>+1, -7/8<br>±1/2                   | ppm of FSR/90<br>LSB<br>LSB                                 |

| CONVERSION SPEED/V models Settling Time to ±0.01% of FSR For FSR Change with 10kΩ Feedback with 5kΩ Feedback For 1LSB Change Slew Rate                                                                                  | 10                         | 5<br>3<br>1.5<br>20           |                                           | 10                         | 5<br>3<br>1.5<br>20           |                                           | μsec<br>μsec<br>μsec<br>V/μsec                              |

| CONVERSION SPEED/I models - of FSR Settling Time to $\pm 0.01\%$ For FSR Change $10\Omega$ to $100\Omega$ Load $1k\Omega$ Load                                                                                          |                            | 300<br>1                      | -                                         |                            | 360<br>1                      |                                           | nsec<br>usec                                                |

| ANALOG OUTPUT/V models Ranges(7) Output Current Output Impedance (DC) Short Circuit Duration                                                                                                                            | ±2.5, ±5<br>±5             | , ±10, 0 to +5,<br>0.05       |                                           | ±5<br>to Common            | 0 to +10<br>0.05              |                                           | Voits<br>mV<br>ohms                                         |

| ANALOG OUTPUT/I models<br>Ranges<br>Output Impedance - Bipolar<br>Output Impedance - Unipolar<br>Compliance                                                                                                             |                            | ±1, 0 to -2<br>4.4<br>15      | ±2.5                                      |                            | 0 to -2<br>4.4<br>15          | ±2.5                                      | mA<br>kΩ<br>kΩ<br>Volts                                     |

| INTERNAL REFERENCE VOLTAGE<br>Maximum External Current(6)<br>Tempco of Drift, max                                                                                                                                       |                            | +6.3<br>±10                   | ±200<br>±20                               |                            | +6.3<br>±10                   | ±200<br>±20                               | Volts<br>μA<br>ppm/°C                                       |

| POWER SUPPLY SENSITIVITY<br>+15V Supply<br>-15V and +5V Supplies                                                                                                                                                        |                            | ±0.02<br>±0.002               | -                                         |                            | ±0.02<br>±0.002               | -                                         | % of FSR/% Vs<br>% of FSR/% Vs                              |

| POWER SUPPLY REQUIREMENTS DAC80 DAC80Z(7) Supply Drain ±15V/±12V (including 5mA load)                                                                                                                                   | ±14, +4.75<br>±11.4, +4.75 | ±15, +5<br>±12, +5<br>±25     | ±16, +16<br>±16, +16<br>±35               | ±14, +4.75<br>±11.4, +4.75 | ±15, +5<br>±12, +5<br>±25     | ±16, +16<br>±16, +16                      | VDC<br>VDG<br>mA                                            |

| +5V (logic supply)  TEMPERATURE RANGE  Specification  Operating (double above specs)                                                                                                                                    | 0<br>-25                   | +20                           | ±30<br>+70<br>+85                         | 0<br>-25                   | +20                           | ±30<br>+70<br>+85                         | mA<br>°C<br>°C                                              |

## NOTES:

- Adding external CMOS hex buffers CD 4009A will provide CMOS input compatibility.

- 2. Adjustable to zero with external trim potentiometer.

- 3. FSR means "Full Scale Range" and is 20V for  $\pm$ 10V range, 10V for  $\pm$ 5V range, etc.

- To maintain drift spec internal feedback resistors must be used for current output models.

- 5. See "Computing Total Accuracy Over Temperature."

- With gain and offset errors adjusted to zero at 25°C. See discussion on last page.

- 7. DAC80Z supply range is  $\pm 12.0V$  min to  $\pm 16.0V$  max for 0 to +10V and  $\pm 10V$  outputs.

- 8. Maximum with no degradation of specifications.

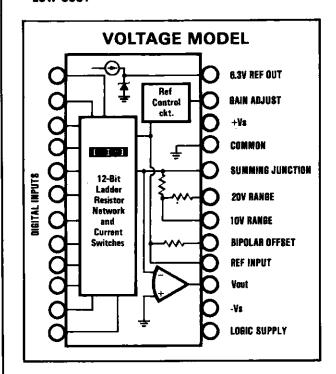

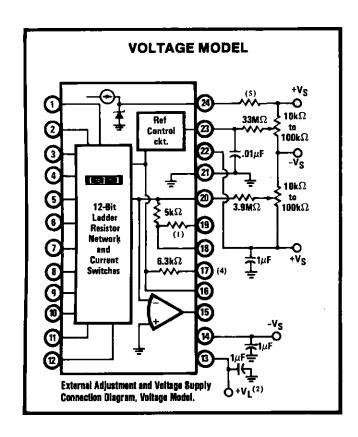

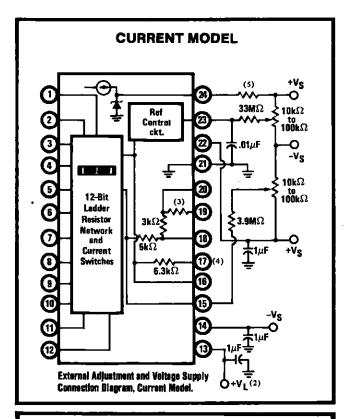

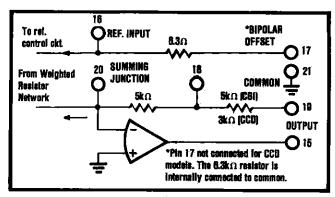

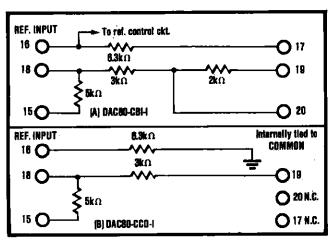

## CONNECTION DIAGRAMS

#### NOTES:

- 1.  $3k\Omega$  for CCD models,  $5k\Omega$  for CBI models.

- 2. If connected to+Vs, which is permissible, power dissipation increases 200mW.

- 3. CBI model,  $2k\Omega;$  CCD model,  $0\Omega$  and pin 20 has no internal connection.

- 4.  $6.3k\Omega$  resistor internally grounded on CCD models.

- 5. Resistor required only for Z models, see "Operating Instructions" Make no connection to power supply on non-Z models.

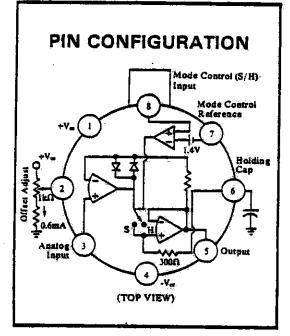

#### **PIN ASSIGNMENTS** Pin i Models No. V Models (MSB) Bit 1 1 Bit 1 (MSB) Bit 2 2 Bit 2 Bit 3 3 Bit 3 Bit 4 4 Bit 4 Bit 5 5 Bit 5 Bit 6 6 Bit 6 Bit 7 Bit 7 Bit 8 8 Bit 8 Bit 9 9 Bit 9 Bit 10 10 Bit 10 Bit 11 Bit 11 11 (LSB) Bit 12 Bit 12 (LSB) 12 LOGIC SUPPLY LOGIC SUPPLY 13 -Vş 14 -Vş 15 Vout lour REF. INPUT REF. INPUT 16 **BIPOLAR OFFSET BIPOLAR OFFSET** 17 SCALING NETWORK 10V RANGE 18 20V RANGE **SCALING NETWORK** 19 SCALING NETWORK 20 **SUMMING JUNCTION** COMMON 21 COMMON +Vs 22 GAIN ADJUST 23 **GAIN ADJUST** 6.3V REF. OUT 6.3V REF. OUT 24

Leads in true position within .010" (.25mm)R at MMC at seating plane.

|     | INC    | HES       | MILLIMETERS |       |  |

|-----|--------|-----------|-------------|-------|--|

| DIM | MIN    | MIN MAX   |             | MAX   |  |

| A   | 1.310  | 1.360     | 33.27       | 34.54 |  |

| 8   | .770   | .810      | 19.56       | 20.57 |  |

| U   | .150   | .210      | 3,81        | 5.33  |  |

| D   | .018   | .021      | 0.46        | 0,53  |  |

| F   | .035   | .050      | 0.89        | 1.27  |  |

| O   | 100 B  | ASIC      | 2.54 B      | ASIC  |  |

| I   | .110   | 130       | 2.79        | 3.30  |  |

| ĸ   | .150   | .250      | 3.81        | 6.35  |  |

| د   | .600 B | 600 BASIC |             | ASIC  |  |

| z   | 002    | .010      | 0.05        | 0.25  |  |

| R   | 085    | 105       | 2.16        | 2.67  |  |

CASE: Ceramic

MATING CONNECTOR: 245MC

PIN: Pin material and plating composition conform to method 2003 (solderability) of MIL-STD-883 (except paragraph 3.2).

WEIGHT: 8.4 grams (0.3 oz.)

HERMETICITY: Conforms to method 1014 condition C step 1 (fluorocarbon) of MIL-STD-883 (gross leak).

## DISCUSSION

#### **DIGITAL INPUT CODES**

The DAC80 accepts complementary digital input codes in either binary (CBI) or decimal (CCD) format. The CBI model may be connected by the user for any one of three complementary codes: CSB, CTC or COB.

TABLE I. Digital Input Codes.

| C          | DIGITAL INPUT ANALOG OUTOUT                                                      |                                                           |                                             |                                            |  |  |  |  |

|------------|----------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------|--------------------------------------------|--|--|--|--|

| odels      | MSB LSB                                                                          | CSB<br>Compl.<br>Straight<br>Binary                       | COB<br>Compl.<br>Offset<br>Binary           | CTC*<br>Compl.<br>Two's<br>Compl.          |  |  |  |  |

| CBI Models | 01111111111<br>100000000000<br>1111111111111                                     | +Full Scale<br>+1/2 Full Scale<br>Mid-scale -1LSB<br>Zero | +Full Scale<br>Zero<br>-1LSB<br>-Full Scale | -LSB<br>-Full Scale<br>-Full Scale<br>Zero |  |  |  |  |

| CCD Models | MSB LSB                                                                          | Complementary                                             | CCD<br>Coded Decim                          | nal - 3 Digits                             |  |  |  |  |

| 000        | 0110 0110 0110<br>1111 1111 1111                                                 | +Full Scale<br>Zero                                       |                                             |                                            |  |  |  |  |

|            | * Invert the MSB of the COB code with an external inverter to obtain.  CTC code. |                                                           |                                             |                                            |  |  |  |  |

#### **ACCURACY**

Linearity of a D/A converter is the true measure of its performance. The linearity error of the DAC80 is specified over its entire temperature range. This means that the analog output will not vary by more than  $\pm 1/2$ LSB, maximum, from an ideal straight line drawn between the end points (inputs all "1"s and all "0"s) over the specified temperature range of 0°C to  $\pm 70$ °C.

Differential linearity error of a D/A converter is the deviation from an ideal 1LSB voltage change from one adjacent output state to the next. A differential linearity error specification of  $\pm 1/2$ LSB means that the output voltage step sizes can range from 1/2LSB to 3/2LSB when the input changes from one adjacent input state to the next.

Monotonicity over a 0°C to +70°C range is guaranteed in the DAC80 to insure that the analog output will increase or remain the same for increasing input digital codes.

## **DRIFT**

Gain Drift is a measure of the change in the full scale range output over temperature expressed in parts per million per °C (ppm/°C). Gain drift is established by: 1) testing the end point differences for each DAC80 model at 0°C, +25°C and +70°C; 2) calculating the gain error with respect to the 25°C value and; 3) dividing by the temperature change. This figure is expressed in ppm/°C and is given in the electrical specifications both with and without internal reference.

Offset Drift is a measure of the actual change in output with all "1"s on the input over the specified temperature range. The offset is measured at 0°C, +25°C and +70°C. The maximum change in Offset is referenced to the Offset

at 25°C and is divided by the temperature range. This drift is expressed in parts per million of full scale range per °C (ppm of FSR/°C).

#### SETTLING TIME

Settling time for each DAC80 model is the total time (including slew time) required for the output to settle within an error band around its final value after a change in input (see Figure 1).

FIGURE 1. Full Scale Range Settling Time vs Accuracy.

Voltage Output Models: Three settling times are specified to ±0.01% of full scale range (FSR); two for maximum full scale range changes of 20V, 10V and one for a 1LSB change. The 1LSB change is measured at the major carry (0111...11 to 1000...00), the point at which the worst case settling time occurs.

Current Output Models: Two settling times are specified to  $\pm 0.01\%$  of FSR. Each is given for current models connected with two different resistive loads:  $10\Omega$  to  $100\Omega$  and  $1000\Omega$  to  $1875\Omega$ . Internal resistors are provided for connecting nominal load resistances of approximately  $1000\Omega$  to  $1800\Omega$  for output voltage range of  $\pm 1V$  and 0 to -2V. See Table IV.

#### COMPLIANCE

Compliance voltage is the maximum voltage swing allowed on the current output node in order to maintain specified accuracy. The maximum compliance voltage of all current output models is  $\pm 2.5$ V. Maximum safe voltage swing permitted without damage to the DAC80 is  $\pm 5$ V.

### POWER SUPPLY SENSITIVITY

Power supply sensitivity is a measure of the effect of a power supply change on the D/A converter output. It is defined as a percent of FSR per percent of change in

either the positive, negative, or logic supplies about the nominal power supply voltages (see Figure 2).

FIGURE 2. Power Supply Rejection vs Power Supply Ripple.

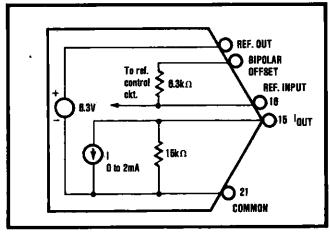

### REFERENCE SUPPLY

All DAC80 models are supplied with an internal 6.3 volt reference voltage supply. This voltage (pin 24) has a tolerance of  $\pm 5\%$  and must be connected to the Reference Input (pin 16) for specified operation. This reference may be used externally also, but external current drain is limited to  $200\mu A$ . An external buffer amplifier is recommended if this reference will be used to drive other system components.

## **OPERATING INSTRUCTIONS**

## **±12 VOLT SUPPLY OPERATION**

The Z models will operate with supply voltages as low as  $\pm 11.4$ V. For operation with supplies less than  $\pm 14$ V an external resistor must be connected between the positive supply and pin 24. This provides additional current required by the internal reference. The required resistor value for supply voltages of  $\pm 11.4$ V to  $\pm 12.6$ V is 2.0k $\Omega$  and for supplies of  $\pm 12.6$ V to  $\pm 14$ V is 3.9k $\Omega$ .

It is recommended that output voltage ranges -10V to +10V and 0 to +10V not be used with the Z model if the supply voltages are ever less than the recommended  $\pm 12V$ . The output amplifier may saturate if  $|V_{\text{supply}}| - |V_{\text{out}}|$  max|< 2.0V. This applies to units with both CBI and CCD input codes. Except for operation at lower supply voltages, the DAC80Z and DAC80 operation is identical.

## **POWER SUPPLY CONNECTIONS**

Decoupling: For optimum performance and noise rejection, power supply decoupling capacitors should be added as shown in the Connection Diagrams. These capacitors ( $1\mu$ F tantalum or electrolytic recommended) should be located close to the DAC80. Electrolytic capacitors, if used, should be paralleled with  $0.01\mu$ F ceramic capacitors for best high frequency performance.

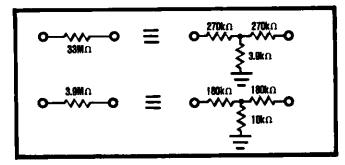

#### EXTERNAL OFFSET AND GAIN ADJUSTMENT

Offset and gain may be trimmed by installing external Offset and Gain potentiometers. Connect these potentiometers as shown in the connection diagrams and adjust as described below. TCR of the potentiometers should be  $100\text{ppm}/^{\circ}\text{C}$  or less. The  $3.9\text{M}\Omega$  and  $33\text{M}\Omega$  resistors (20% carbon or better) should be located close to the DAC80 to prevent noise pickup. If it is not convenient to use these high value resistors, an equivalent "T" network, as shown in Figure 3, may be substituted in each case. The Gain Adjust (pin 23) is a high impedance point and a  $0.001\mu\text{F}$  to  $0.01\mu\text{F}$  ceramic capacitor should be connected from this pin to Common (pin 21) to prevent noise pickup. Refer to Figures 4 and 5 for relationship of Offset and Gain adjustments to unipolar and bipolar D/A converters.

Offset Adjustment: For unipolar (CSB, CCD) configurations, apply the digital input code that should produce zero potential output and adjust the Offset potentiometer for zero output.

FIGURE 3. Equivalent Resistance.

For bipolar (COB, CTC) configurations, apply the digital input code that should produce the maximum negative output voltage. Example: If the Full Scale Range is connected for 20V, the maximum negative output voltage is -10V. See Table II for corresponding codes and the Connection Diagrams for offset adjustment connections.

FIGURE 4. Relationship of Offset and Gain Adjustments for a Unipolar D/A Converter.

TABLE II. Digital Input/Analog Output.

|            |                                                                                                                    |                                                       | ANALOG                                                 | OUTPUT                                                     |                                                           |

|------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|

| ı          | DIGITAL INPUT                                                                                                      | VOLT                                                  | TAGE*                                                  | CURI                                                       | RENT                                                      |

|            |                                                                                                                    | 0 to +10V                                             | ±10V                                                   | 0 to -2mA                                                  | ±1mA                                                      |

| CBI Models | 12-Bit Resolution<br>MSB LSB<br>000000000000<br>011111111111<br>10000000000                                        | +9.9976V<br>+5.0000V<br>+4.9976V<br>0.0000V<br>2.44mV | +9.9951V<br>0.0000V<br>-0.0049V<br>-10.0000V<br>4.88mV | -1.9995mA<br>-1.0000mA<br>-0.9995mA<br>0.0000mA<br>0.488µA | -0.9995mA<br>0.0000mA<br>+0.0005mA<br>+1.000mA<br>0.488µA |

| CCD Models | 3-Digital Resolution<br>MSB LSB<br>0110 0110 0110<br>0110 0110 1111<br>0110 1111 1111<br>1111 1111 1111<br>One LSB | +9.990V**<br>+9.900V<br>+9.000V<br>0.000V<br>10.00mV  | N/A<br>N/A<br>N/A<br>N/A<br>N/A                        | -1.249mA<br>-1.238mA<br>-1.125mA<br>0.000mA<br>• 1.25µA    | N/A<br>N/A<br>N/A<br>N/A<br>N/A                           |

<sup>\*</sup>To obtain values for other binary (CBI) ranges: 0 to +5V range: divide 0 to +10V range values by 2.  $\pm$ 5V range: divide  $\pm$ 10V range values by 2.

±2.5V range: divide ±10V range values by 4.

Gain Adjustment: For either unipolar or bipolar configurations, apply the digital input that should give the maximum positive voltage output. Adjust the Gain potentiometer for this positive full scale voltage. See Table II for positive full scale voltages and the Connection Diagrams for gain adjustment connections.

FIGURE 5. Relationship of Offset and Gain Adjustments for a Bipolar D/A Converter.

## **VOLTAGE OUTPUT MODELS**

### **OUTPUT RANGE CONNECTIONS**

Internal scaling resistors provided in the DAC80 may be connected to produce bipolar output voltage ranges of  $\pm 10V^*$ ,  $\pm 5V$  or  $\pm 2.5V$  or unipolar output voltage ranges of 0 to  $\pm 5V$  or 0 to  $\pm 10V^*$ . See Figure 6.

FIGURE 6. Output Amplifier Voltage Range Scaling Circuit.

Gain and offset drift are minimized in the DAC80 because of the thermal tracking of the scaling resistors with other device components. Connections for various output voltage ranges are shown in Table III. Settling time is specified for a full scale range change: 5 microseconds for  $8k\Omega$  or  $10k\Omega$  feedback resistors; 3 microseconds for a  $5k\Omega$  feedback resistor.

TABLE III. Output Voltage Range Connections - Voltage Model DAC80.

| Output<br>Range | Digital<br>Input Codes |    |      | Connect<br>Pin 19 to |    |

|-----------------|------------------------|----|------|----------------------|----|

| ±10             | COB or CTC             | 19 | 20   | 15                   | 24 |

| ±5              | COB or CTC             | 18 | 20   | N.C.                 | 24 |

| ±2.5V           | COB or CTC             | 18 | 20   | 20                   | 24 |

| 0 to +10V       | CSB                    | 18 | 21.  | N.C.                 | 24 |

| 0 to +5V        | CSB                    | 18 | 21   | 20                   | 24 |

| 0 to +10V       | CCD                    | 19 | N.C. | 15                   | 24 |

| _               |                        |    |      |                      |    |

<sup>\*\*</sup>Normal Full Scale Range with correct codes; output can go higher if illegal codes are applied.

<sup>\*</sup>Refer to ±12V Supply Operation discussion.

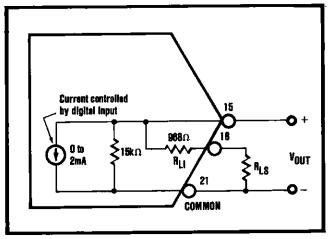

## **CURRENT OUTPUT MODELS**

The equivalent output circuit and resistive scaling network of the current model differ from the voltage model and are shown in Figures 7 and 8. Instructions for using the DAC80-XXX-I with a resistor or an external op amp follow. External  $R_{LS}$  or  $R_{LP}$  resistors are required to produce exactly 0 to -2V or  $\pm 1$ V output. TCR of these resistors should be  $\pm 100 \text{ppm}/^{\circ}\text{C}$  or less to maintain the DAC80 output specifications. If exact output ranges are not required, the external resistors are not needed.

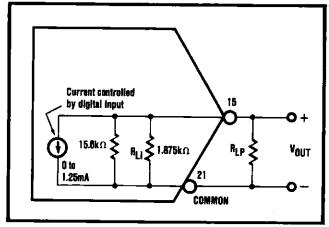

FIGURE 7. Internal Scaling Resistors.

Internal resistors are provided to scale an external op amp or to configure a resistive load to offer two output voltage ranges of  $\pm 1 \text{V}$  or 0 to -2V. These resistors (R<sub>LI</sub>) are an integral part of the DAC80 and maintain gain and bipolar offset drift specifications. If the internal resistors are not used, external R<sub>L</sub> (or R<sub>F</sub>) resistors should have a TCR of  $\pm 25$  ppm/°C or less to minimize drift. This will typically add  $\pm 50$  ppm/°C+ the TCR of R<sub>L</sub> (or R<sub>F</sub>) to the total drift.

FIGURE 8. DAC80 Current Model Equivalent Output Circuit.

#### **DRIVING A RESISTIVE LOAD UNIPOLAR**

A load resistance,  $R_L = R_{LI} + R_{LS}$ , connected as shown in Figure 9 will generate a voltage range,  $V_{OUT}$ , determined by:

$$V_{OUT} = -2mA \qquad \left(\frac{15k\Omega \times R_L}{15k\Omega + R_L}\right)$$

Where  $R_L$  max = 1.36k $\Omega$  and  $V_{OUT}$  max = -2.5V

To achieve specified drift, connect the internal scaling resistor ( $R_{LI}$ ) as shown in Table IV to an external metal film trim resistor ( $R_{LS}$ ) to provide full scale output voltage range of 0 to -2V. With  $R_{LS} = 0$ ,  $V_{OUT} = -1.82V$ .

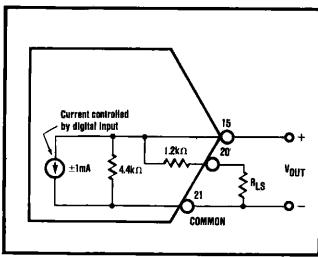

CCD Input Code: Connect the internal scaling resistors as shown in Table IV and add an external metal film

FIGURE 9. Equivalent Circuit DAC80-CB1-I

Connected for Unipolar Voltage Output

with Resistive Load.

TABLE IV, DAC80-XXX-I Resistive Load Connections.

|                        |                 | Internal                      | 1% M∈                       | etal Film                     | RL                   | Connecti             | ons  | Reference            |                      | Bipolar Offset                  |                 |

|------------------------|-----------------|-------------------------------|-----------------------------|-------------------------------|----------------------|----------------------|------|----------------------|----------------------|---------------------------------|-----------------|

| Digital<br>Input Codes | Output<br>Range | Resistance<br>R <sub>LÍ</sub> | External<br>R <sub>LS</sub> | Resistance<br>R <sub>LP</sub> | Connect<br>Pin 15 to |                      |      | Connect<br>Pin 16 to | Connect<br>Pin 17 to | RLS                             | R <sub>LP</sub> |

| CSB                    | 0 to -2V        | 0.968kΩ                       | 105Ω                        | N/A                           | 20                   | 19 & R <sub>LS</sub> | 15   | 24                   | Com (21)             | Between<br>Pin 18 &<br>Com (21) | N/A<br>Between  |

| CCD                    | 0 to -2V        | 1.875kΩ                       | N/A                         | 36.5kΩ                        | 19                   | Com (21)             | N.C. | 24                   | N.C                  | N/A<br>Between                  | Pin 15 & 21     |

| COB or CTC             | ±1V             | 1.2kΩ                         | 90.90                       | N/A                           | 18                   | 19                   | RLS  | 24                   | 15                   | Pin 20 &<br>Com (21)            | N/A             |

resistor (R<sub>LP</sub>) in parallel as shown in Figure 10 to obtain a 0 to -2V full scale output voltage range for CCD input codes:

With

$$R_L = \frac{R_{LI} \times R_{LP}}{R_{LI} + R_{LP}}$$

$$V_{OUT} = -1.25 \text{mA} \left( \frac{15.6 \text{k}\Omega \times R_L}{15.6 \text{k}\Omega + R_L} \right)$$

If  $R_{LP} = \infty$ ,  $V_{OUT} = -2.08 \text{V}$

FIGURE 10. DAC80-CCD-I Connected for Voltage Output with Resistive Load.

## DRIVING A RESISTOR LOAD BIPOLAR

The equivalent outtut circuit for a bipolar output voltage range is shown in Figure 11,  $R_L = R_{L1} + R_{LS}$ .  $V_{OUT}$  is determined by:

$$\begin{split} V_{OUT} &= \pm 1 \, mA \quad \left( \frac{R_L \; x \; 4.44 k\Omega}{R_L + 4.44 k\Omega} \right) \\ Where \; R_L \; max &= 5.72 k\Omega \\ V_{OUT} \; max &= \pm 2.5 V \end{split}$$

To achieve specified drift, connect the internal scaling resistors ( $R_{LI}$ ) as shown in Table IV for the COB or CTC

FIGURE 11. DAC80-CBI-I Connected for Bipolar

Output Voltage with Resistive Load.

codes and add an external metal film resistor ( $R_{LS}$ ) in series to obtain a full scale output range of  $\pm 1V$ .

With

$$R_{LS} = 0$$

,  $V_{OUT} = \pm 0.944 V$ .

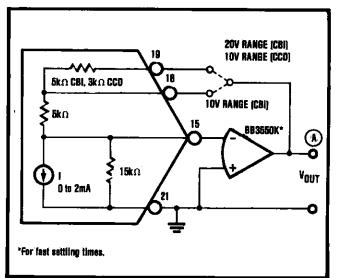

#### DRIVING AN EXTERNAL OF AMP

The current model DAC80 will drive the summing junction of an op amp used as a current to voltage converter to produce an output voltage. See Figure 12.

$$V_{OUT} = I_{OUT} \times R_F$$

where Iour is the DAC80 output current and R<sub>F</sub> is the feedback resistor. Using the internal feedback resistors of the current model DAC80 provides output voltage ranges the same as the voltage model DAC80. To obtain the desired output voltage range when connecting an external op amp, refer to Table V.

TABLE V. Voltage Range of Current Output DAC80.

| Output<br>Range | Input Codes | _  |      | Connect<br>Pin 19 to |    |

|-----------------|-------------|----|------|----------------------|----|

| ±10V.           | COB or CTC  | 19 | 15   | A                    | 24 |

| ±5V             | COB or CTC  | 18 | 15   | M.C.                 | 24 |

| ±2.5V           | COB or CTC  | 18 | 15   | 15                   | 24 |

| 0 to +10V       | CSB         | 18 | 21   | N.C.                 | 24 |

| 0 to +5V        | CSB         | 18 | 21   | 15                   | 24 |

| 0 to +10V       | CCD         | 19 | N.C. | 8                    | 24 |

FIGURE 12. External Op Amp - Using Internal Feedback Resistors.

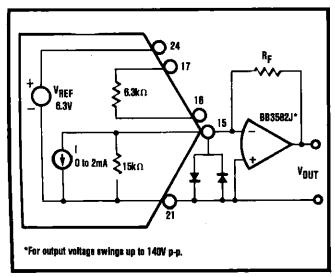

## **OUTPUT LARGER THAN 20V RANGE**

For output voltage ranges larger than  $\pm 10V$ , a high voltage op amp may be employed with an external feedback resistor. Use  $l_{OUT}$  values of  $\pm 1$ mA for bipolar voltage ranges and -2mA for unipolar voltage ranges. See Figure 13. Use protection diodes when a high voltage op amp is used.

The feedback resistor,  $R_F$ , should have a temperature coefficient as low as possible. Using an external feedback resistor, overall drift of the circuit increases due to the

lack of temperature tracking between  $R_F$  and the internal scaling resistor network. This will typically add 50 ppm/°C +  $R_F$  drift to total drift.

FIGURE 13. External Op Amp - Using External Feedback Resistors.

# COMPUTING TOTAL ACCURACY OVER TEMPERATURE

The accuracy drift with temperature of a DAC80 consists of three primary components: Gain drift, unipolar or bipolar offset drift, and linearity drift. To obtain the worst case accuracy drift, most users would assume that all drift errors are random and would simply add them algebraically. However, the worst case accuracy drift for a DAC80 operating in the bipolar mode is about one-half of the algebraic sum of the individual drift errors.

To explain this fact, it is necessary to consider the unipolar and bipolar modes of operation separately. Note that the linearity drift of both modes is negligible. (Total linearity error is less than  $\pm 1/2$ LSB over 0°C to  $\pm 70$ °C.)

In the unipolar mode of operation, offset drift ( $\pm 1$  ppm/°C) is due primarily to voltage offset drift of the output op amp and, to a lesser extent, to the leakage current through the quad current switches. Gain drift consists of several components: 1)  $\pm 10$  ppm/°C due to ratio drift of current weighting resistors to the reference resistor and current switch  $V_{BE}$  to the reference transistor (refer to Model 4550 data sheet); and 2)  $\pm 20$  ppm/°C due to the zener reference. The sum of these two components,  $\pm 30$  ppm/°C, is the maximum gain drift.

Because the parameters described could all drift in the same direction, the worst case accuracy drift in the unipolar mode is simply the sum of the components, or  $\pm 31 \text{ ppm}/^{\circ}\text{C}$ .

In the bipolar mode the major portion (67%) of gain drift is due to the zener reference. The gain and offset drifts caused by reference drift are always in opposite

directions. Therefore, the accuracy drift will be the difference rather than the sum of these drifts.

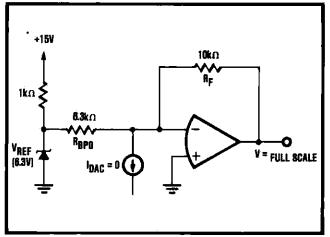

First, consider the effect of reference variations on offset drift. Figure 14 shows a simplified circuit diagram of a DAC80 operating in the bipolar mode with all bits off. The current switch leakage current is negligible, so

$$V_{\text{-FULL SCALE}} = -\frac{R_F}{R_{BPO}} \times V_{REF}$$

$$= -\frac{10k\Omega}{6.3k\Omega} \bullet 6.3V = -10V$$

FIGURE 14. Simplified Diagram of DAC80 with "All Bits Off" Operating in Bipolar ±10V Range.

This equation shows that if  $V_{REF}$  increases, the output voltage will decrease and vice versa. If the  $V_{REF}$  drift is +20 ppm/°C, this is equivalent to (+20 ppm/°C) x  $(+6.3V) = +126\mu V$ /°C. This will result in a voltage drift at the amplifier output of

$$\begin{split} \frac{\Delta V_{\text{-FS}}}{\Delta T} &= -\frac{R_F}{R_{BPO}} \bullet \frac{\Delta V_{REF}}{\Delta T} \\ &= -\frac{10 k \Omega}{6.3 k \Omega} \bullet 126 \mu V/^{\circ} C = -200 \mu V/^{\circ} C. \end{split}$$

Since the DAC80 is operating in the  $\pm 10V$  range this is equivalent to  $(-200\mu V)^{\circ}C) \div (20V \text{ range}) = -10 \text{ ppm of } FSR/^{\circ}C$ .

Now consider the effect of reference changes on gain drift. When all the bits are turned on it can be shown that:

$$\begin{split} \frac{\Delta V_{+\text{FULL SCALE}}}{\Delta T} &= + \quad \frac{R_F}{R_{BPO}} \bullet \frac{V_{REF}}{\Delta T} \\ = + & \frac{10 k \Omega}{6.3 k \Omega} \bullet 126 \mu V/^{\circ} C = +200 \mu V/^{\circ} C \\ \text{and} & \frac{+200 \mu V/^{\circ} C}{20 V \text{ Range}} = +10 \text{ppm/}^{\circ} C \text{ of FSR.} \end{split}$$

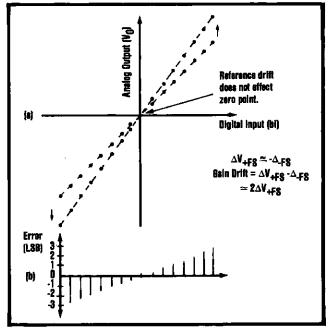

This result indicates that the drift of the minus full scale voltage will be equal in magnitude to, and in the opposite direction of, the drift of the plus full scale voltage and that zener reference variations have virtually no effect on the zero point (see Figure 15). This equation also indicates that the gain drift is equal to the  $V_{REF}$  drift in ppm/°C, and the magnitude of the minus full scale drift and plus full scale drift is equal to one-half of the  $V_{REF}$  drift.

FIGURE 15. (a) Effect of a Positive Reference Drift on the Ideal D/A Transfer Function; (b) Error Distribution Due to Reference Voltage Drift in a DAC80.

Using this relationship, the worst case accuracy drift for a bipolar DAC80 can be computed. The maximum TCR of the zener reference is  $\pm 20$ ppm/°C. The gain drift due to the reference then is also  $\pm 20$ ppm/°C. The full scale drift and bipolar offset drift are each half that amount or ±10ppm/°C. The maximum gain and offset drifts of the DAC80, exclusive of the reference, are ±10ppm/°C and ±5ppm/°C respectively. Adding this to the full scale drift due to the reference gives a worst case total accuracy drift of ±25ppm/°C. (Random drifts, which these are, can be in the same direction, so they add directly.) This is much less than the total drift obtained by simply adding the maximum gain and bipolar offset drifts (±45ppm/°C). The maximum zero point drift is equal to one-half of the gain drift exclusive of the reference plus the offset drift exclusive of the reference, or ±10ppm of FSR/°C.

The DAC80 is specified over a 0°C to +70°C temperature range giving a maximum excursion from room temperature (+25°C) of 45°C. Assuming that gain and offset errors have been adjusted to zero at room temperature,

total worst case accuracy error

- = Linearity error + Accuracy drift x ΔT

- $=\pm0.01\% + \pm25$ ppm/°C (45°C)(100)

- $=\pm0.12\%$ ;

total worst case bipolar zero point error

- = Bipolar zero drift  $x \Delta T$

- $= \pm 10$ ppm of FSR% (45°C)(100)

- $=\pm0.045\%$ .

#### **ORDERING INFORMATION** DAC80 OUTPUT **INPUT CODE** Low Cost 12-Bit D/A Converter Z = Wide SupplyCBI = Complementary Family Range V = VoltageBlank = Standard 12-bit binary Example: DAC80-CBI-V I = Current CCD = ComplementaryBinary DAC80 3-digit BCD with voltage output

# Company Control (my Control

## SHC298AM

dupa.

# LOW COST MONOLITHIC SAMPLE-HOLD AMPLIFIER

- 12 Bit Throughput Accuracy

- Less Than 10 page Acquisition Time

- Wideband Noise Lass Than 20 µV rms

- Reliable Monolithic Construction

- 1010 Ω input Resistance

- TTL/PMOS/CMOS Compatible Logic Input

## DESCRIPTION

The SHC298AM is a high performance monolithic sample/hold circuit which features very high DC accuracy with fast acquisition times and a low droop rate. With the addition of one external holding capacitor, 12 bit accuracy can be achieved with a 6 microsecond acquisition time. Droop rates less than 5 millivolts per minute can be achieved with a one microfarad holding capacitor.

The fully differential logic inputs have low input currents, and are compatible with TTL, PMOS, and CMOS logic families. The input offset adjustment can be made using a single external potentiometer and resistor, and the adjustment does not degrade input offset drift.

The SHC298AM will operate with power supplies ranging from ±5 volts to ±18 volts. It is available in a hermetically sealed 8 lead low profile package, and is specified for a temperature range from -25 to +85°C. The SHC298AM is the best price/performance bargain in its class. It is well suited for use in data acquisition systems, data distribution systems, analog delay circuits, and pulse amplitude modulation circuits.

Control of the contro

BURR-BROWN

International Airport Industrial Park+P.O. Sox 11400-Tucson, Arizona 85734 Tel: 802-294-1431 - Twx: 910-952-1111 - Cable: 888CORP - Telex: 88-6491

Late: acquisition: systems/date: converters.

Date: acquisition: systems/date: converters.

Date: occupipeses: periodents/dower. Synties.

# **SPECIFICATIONS**

Specifications at Ta = +25°C with rated supplies with 1000 pF holding canacitor unless otherwise revert

| Specifications at T <sub>A</sub> = +25°C with rated supplies with 1000 pF holding capacitor unless of |                                              |                  |               |                |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------|---------------|----------------|

| ELECTRICAL                                                                                            |                                              |                  |               |                |

| MODELS                                                                                                |                                              | SHC298AM         |               |                |

| INPUT                                                                                                 | MIN                                          | TYP              | MAX           | UNITS          |

|                                                                                                       | <del></del>                                  |                  | <del></del>   | <del></del>    |

| ANALOG INPUT Voltage Range                                                                            | ±(Vcc-2.5                                    | J                | ļ             |                |

| Maximum Safe Input Signal                                                                             | 2, voc-22                                    | ±V <sub>00</sub> | [             | Voits<br>Voits |

| Resistance<br>Bias Current                                                                            |                                              | 10,0             | 50            | Ohms           |

| DIGITAL INPUT                                                                                         | Pin 7                                        | Pin 8            | Circuit Sta   |                |

| Mode Control Truth Table                                                                              | ov                                           | +2.4V            | Sample (Tr    | **             |

|                                                                                                       | 0V<br>+24V                                   | +0.8V<br>+2.8V   | Hold<br>Hold  |                |

| Mode Control and Mode Control                                                                         | +0.8V                                        | +2.8V            | Sample (Tr    | uck)           |

| Reference Input Current                                                                               |                                              |                  | 10            | l µA           |

| Differential Logic Threshold                                                                          | <u> </u>                                     | 1.4              | <u> </u>      | Volts          |

| TRANSFER CHARACTERISTIC                                                                               | 2                                            | <del>,</del>     | ,             | <del>,</del>   |

| ACCURACY (25°) Throughout Nonlinearity                                                                |                                              | İ                | 1             |                |

| for Hold Time < 1ms                                                                                   |                                              | #0.010           | ±0.015        | % of 20V       |

| Gain<br>Gain Error                                                                                    | ]                                            | +i.0<br>±0.004   | ±0.010        | V/V            |

| Input Voltage Offset (adj to zero) Droop Rate                                                         | ĺ                                            | ±2<br>±25        | ±7<br>±125    | mV             |

| Charge Office                                                                                         | }                                            | #15              | ±25           | μV/mat<br>mxV  |

| Noise (rms) 10 Hz to 100 kHz<br>Power Supply Rejection                                                |                                              | ±25              | 20<br>±50     | μV<br>μV/V     |

| ACCURACY DRIFT                                                                                        |                                              |                  | <u> </u>      |                |

| Gain Drift Input Offset Drift                                                                         |                                              | 3<br>15          | 45            | ppm/°C         |

| Charge Offset Drift C = 1000 pF                                                                       |                                              | 50               | 150           | μV/°C<br>μV/°C |

| C = 10,000 pF<br>Droop Rate at T <sub>A</sub> = +85°C                                                 |                                              | 20<br>!          | 50<br>[0      | μV/°C          |

| DYNAMIC CHARACTERISTICS                                                                               |                                              |                  |               |                |

| Full Power Bandwidth, C = 1000 pF                                                                     | 75                                           | 125              | 1             | kHz            |

| C = 10,000 pF<br>Output Slew Race, C = 1000 pF                                                        | 10<br>7                                      | 16<br>10         |               | kHz<br>V/μs    |

| C = 19,000 pF<br>Aperaire Time                                                                        | 1.4                                          | 2                |               | V/μα           |

| Negative Input Step Positive Input Step                                                               |                                              | 125<br>30        | 200<br>45     | ns.            |

| Acquisition Time ( $C = 1000 \text{ pF}$ )                                                            |                                              |                  |               | TRB:           |

| to ±0.01%, 10V step<br>to ±0.01%, 20V step                                                            |                                              | 6<br>8           | 10<br>12      | 778<br>178     |

| to ± 0.1%, 10V step<br>to ±0.1%, 20V step                                                             |                                              | 5<br>7           | g<br>II       | 24<br>24       |

| Sample-to-Hold Transient Peak Amplitude                                                               |                                              | 160              | "             |                |

| Settling to 1 mV                                                                                      | <u>.                                    </u> | 1.0              | 1.5           | æV<br>µ≰       |

| Feedthrough (Response to 10V Input.)                                                                  | orep)                                        | ±0.007           | ±0.015        | % of 20V       |

| OUTPUT                                                                                                | · · · · · · · · · · · · · · · · · · ·        |                  | <del>,,</del> |                |

| ANALOG OUTPUT                                                                                         | -W 20                                        |                  |               |                |

| Voitage Range<br>Current Range                                                                        | ±(V=-5'2)                                    |                  |               | Volta<br>mA    |

| Impedance                                                                                             |                                              | 0.5              | 4             | Ohms           |

| TEMPERATURE Specification                                                                             |                                              | 47               | 1             |                |

| Operating                                                                                             | -25 to ±65<br>-55 to +125                    |                  |               | ಗೆನೆನ          |