# CA-24 Solderless Prototyping Board Experimenter's Manual

© Ohio Scientific August, 1981 Copyright 1981 by Ohio Scientific Inc. All rights reserved. This book or any part thereof, may not be reproduced without the permission of the publishers. Although great care has been taken in the preparation of this operations manual to insure the technical correctness, no responsibility is assumed by Ohio Scientific for any consequences resulting from the use of its contents. Nor does Ohio Scientific assume any responsibility for any infringements of patents or other rights of third parties which may result from its use. If you discover misprints or errors please send a letter to the attention of: Documentation Department, Ohio Scientific Inc., 1333 S. Chillicothe Road, Aurora, Ohio, 44202.

#### **PREFACE**

The CA-24 experimenters board can be a useful learning device for the novice, or it can be a sophistocated tool for the person experienced in computer hardware. If you need an introduction to (or a review of) digital electronics, Section II of this manual will lead you through a series of experiments dealing with gates, flip-flops, and the monostable multivibrator. A computer is not needed for these experiments. If you are already experienced in electronics, Experiments 1, 2, and 3 will introduce you to the operation of the board which you then can use as a stand alone device for breadboarding simple to highly complex analog as well as digital circuits. In either case, of course, you should read Section I which contains a description of the various features of the board.

Section III of this manual contains a series of experiments which leads you through the use of the board as an interactive device with an OSI computer. For these experiments, you must have an OSI C4PMF, C4PDF, or C8PDF computer. (A C1PMF can be used if it has the 630 I/O board installed.) Both general use and specific applications are covered. Since the applications in the experiments are for the purpose of illustration rather than as ends in themselves, simplicity within each experiment is stressed.

When the CA-24 board is used with a computer, a certain amount of programming is necessary. Whenever possible, the experiments in this manual which involve interfacing with a computer include programs written in the computer language BASIC. This high level language facilitates convenient and rapid programming. In one experiment, which requires high resolution timing, assembly language routines (with their accompanying machine codes) have been used to provide the necessary speed and flexibility. These routines are explained in detail.

Once you have worked through the experiments, you should be able to use the CA-24 board creatively for a wide range of applications. If you find you need more background in electronics, a bibliography listing several introductory electronics and 6502 assembly language textbooks and manuals is included in Appendix 2.

This manual has been produced by the cooperative effort of many people. The principal organization and writing of the manual in its present form was accomplished by Dr. Lawrence C. Becker, Professor of Physics at Hiram College. Most of the ideas for the experiments, however, were generated by Dr. Louis E. Roemer, Professor of Engineering at the University of Akron. The diagrams and figures (with the exception of Figures 3A and 3B) were put into final form by Craig Bair, a student at Hiram College. Much credit goes to Cookie Beck, the Physics Department secretary at Hiram College, who trained herself on the OSI word processor and put the text of the manual on disk storage. Her enthusiasm and optimism were an encouragement and her attention to accuracy and consistency caught numerous errors during the typing of the text. Julie Maston, a student worker in the secretarial office, helped with the disk storage process.

Careful and extensive proof reading and user testing were performed by Dr. Stewart Becker (retired Professor of Electrical Engineering at the University of Arizona); Dr. Darrell Turnidge, Dr. J. P. Neuzil, and Dr. Victor Nicholson (Associate Professors of Mathematics at Kent State University); Dr. Edward Carlson (Professor of Physics at Michigan State University); Dr. Michael Grajek (Associate Professor of Mathematics at Hiram College); Morgan Paul (student at Hiram College); and Paul Joviak (Systems Programmer at Ohio Scientific). Their corrections and suggestions have been valuable contributions to the final form of this manual.

Finally, the encouragement and patience of David Loynd (Product Support Manager at Ohio Scientific) who initiated the project and has overseen each phase of its development should not go unrecognized. His persistence and direction have successfully guided the project to its conclusion.

# TABLE OF CONTENTS

| PREFACE i                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------|

| PARTS AND TOOLS LISTiv                                                                                                      |

| FIGURE LIST vi                                                                                                              |

| SECTION I. DESCRIPTION AND USES OF THE CA-24 EXPERIMENTER'S BOARD Stand-Alone Breadboard 1 Computer Interfaced Breadboard 7 |

| SECTION II. EXPERIMENTS USING ONLY THE CA-24 BOARD                                                                          |

| Overview and Power Supply Connection 8 Experiment 1: LED Indicators 10                                                      |

| Experiment 1: LED Indicators 10                                                                                             |

| Experiment 2: Logic Level Switches 14                                                                                       |

| Experiment 3: Adjustable Frequency Clock 17                                                                                 |

| Experiment 4: AND Gate 22                                                                                                   |

| Experiment 5: NAND Gate and Inverter 28                                                                                     |

| Experiment 6: NOR Gate and Inverter 35                                                                                      |

| Experiment 7: OR Gate from NOR Gates 41                                                                                     |

| Experiment 8: Exclusive OR Gate from AND, NAND, and NOR Gates - 45                                                          |

| Experiment 9: The R-S Flip-Flop (RSFF) 49                                                                                   |

| Experiment 10: The D Flip-Flop (74175) 57                                                                                   |

| Experiment 11: 3-State Quad Bus Transceiver (8T28) 61                                                                       |

| Experiment 12: Contact Bounce and the Monostable Multivibrator                                                              |

| or One-Shot (74121) 67                                                                                                      |

| SECTION III. EXPERIMENTS USING THE CA-24 BOARD AND AN OSI MICROCOMPUTE                                                      |

| Overview 79                                                                                                                 |

| Computer Connection82                                                                                                       |

| Experiment 13: Use of CA-24 Board Latches: Output 85                                                                        |

| Experiment 13: Use of CA-24 Board Latches: Untput 91                                                                        |

| Experiment 14: Use of CA-24 Board Latenes: Input 91 Experiment 15: Computer Routing of Data 96                              |

| Experiment 15: Computer Routing of Data 96  Experiment 16: The CA-24 Board Peripheral Interface                             |

| Adapter (PIA) 98                                                                                                            |

| Experiment 17: Use of Additional PIA's 106                                                                                  |

|                                                                                                                             |

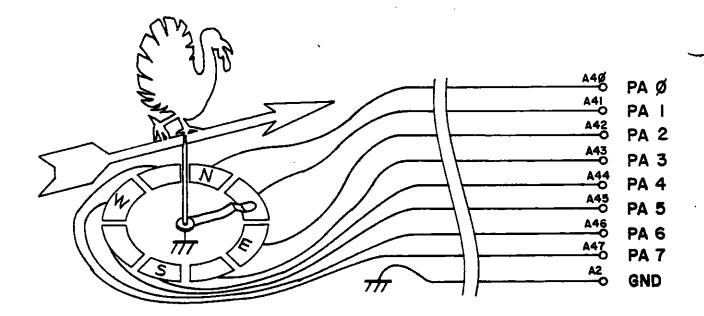

| Experiment 18: Interfacing the Computer With a Weathervane 109                                                              |

| Experiment 19: Interfacing the Computer With a Keyboard 113                                                                 |

| Experiment 20: Interfacing the Computer With a Linear Air Track                                                             |

| Photogate: Machine Language Programming 117 Experiment 21: Parallel to Serial Conversion and the                            |

|                                                                                                                             |

| Asynchronous Communication Interface                                                                                        |

| Adapter (ACIA)                                                                                                              |

| Experiment 22: Analog to Digital Conversion 142                                                                             |

| Experiment 23: Digital to Analog Conversion 148                                                                             |

| SECTION IV. APPENDICES                                                                                                      |

| 1. Integrated circuits specification sheets 157                                                                             |

| 2. Bibliographydigital electronics and 6502                                                                                 |

|                                                                                                                             |

| assembly language books                                                                                                     |

| assembly language books                                                                                                     |

| assembly language books $171$<br>3. Tear sheetsreference copies of schematics and                                           |

| assembly language books                                                                                                     |

# PARTS AND TOOLS LIST

This manual is designed to be used with the Ohio Scientific CA-24 Solderless Interface Prototyping Board. Experiments 1 - 12 require only that the CA-24 board be connected to an adequate power supply. Section II, page 8 discusses the power supply requirements of the CA-24 board. Experiments 13 - 23 require that the CA-24 board be interfaced with either a C4P or C8P using a 16 pin ribbon cable. Section III, page 82 of this manual describes how to make this connection.

The following is a list of the components provided with this manual. You should identify each of these components before beginning to work through this manual.

IC Chips (The IC Chips provided with this manual have a black rectangular top approximately one or two inches long with a row of metal pins extending from both sides. The identification numbers on the IC chips are clearly marked on their top surface. Page 23 describes how to identify pin one on an IC chip.)

68B21 PIA Chip MC685Ø ACIA Chip 74ØØ IC Chip 74Ø2 IC Chip 74Ø8 IC Chip 74121 IC Chip 74175 IC Chip 8T28 IC Chip 339A IC Chip

Resistors (The resistors provided with this manual are mounted in the center of wires approximately 2 1/2 inches long. The resistors themselves are approximately 1/4 inch long and 1/8 inch in diameter. The value of a resistor is specified by a pattern of color bands. There is a row of 32 resistors along the front edge of the CA-24 board.)

- 5 l kilo Ohm resistors ( brown black red gold

- 4 2 kilo Ohm resistors ( red black red gold )

- 1 33 kilo Ohm resistor ( orange orange gold )

10 micro Farad capacitor (The metal cased capacitor is labeled 10 M F and has the + (or -) lead labeled.)

Jumper Wires (20 each)

Short wires (2 inches)

Medium wires (4 inches)

Long wires (8 inches)

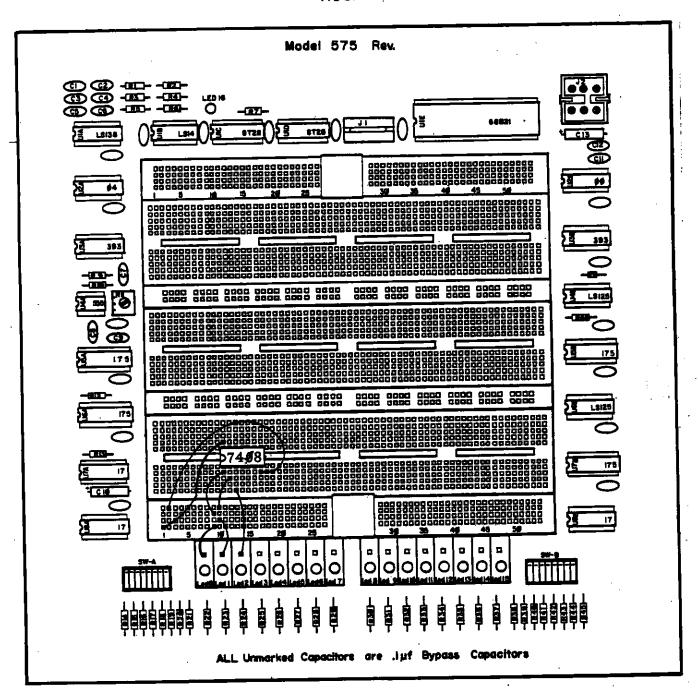

- 5 kilo Ohm potentiometer (This is a duplicate of the part labeled R11 on the CA-24 board. See Fig. 1, page 2.)

- DIP Switch (This is a block of 8 SPST switches. It is a duplicate of the parts labeled SW-A and SW-B on the CA-24 board. See Fig. 1, page 2.)

A small screwdriver is required for removing IC chips and adjusting the potentiometer. Experiment 23 (the last experiment) requires the use of a voltmeter. Experiment 3 describes how an (optional) oscilloscope can be attached to the CA-24 board if one is available. In some of the experiments you may find the use of a digital logic probe to be helpful in tracing the actual signals on the board. Inexpensive logic probes can be purchased at electronics stores for approximately \$25.

# FIGURE LIST

|     | Page<br>Number | Caption                                                          |  |  |

|-----|----------------|------------------------------------------------------------------|--|--|

| 1   | 2              | Terminal strip labeling                                          |  |  |

| 2   | 3              | Under-side terminal connections                                  |  |  |

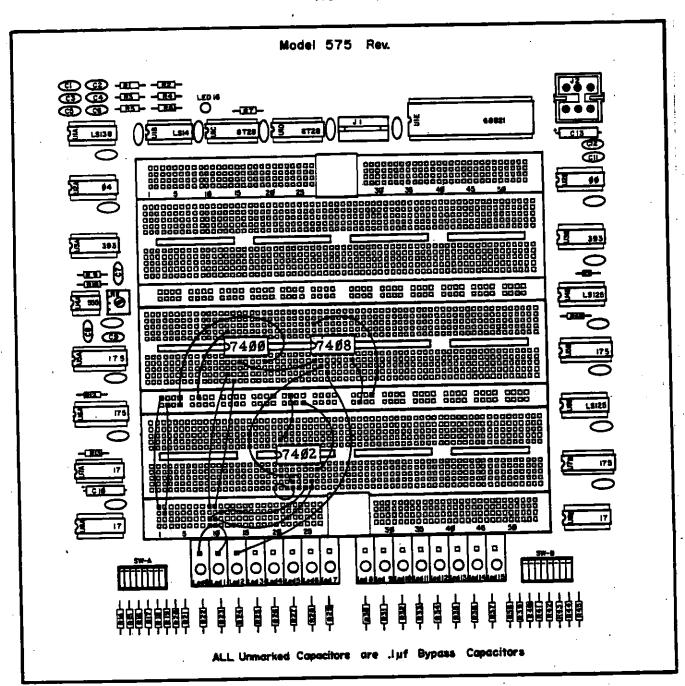

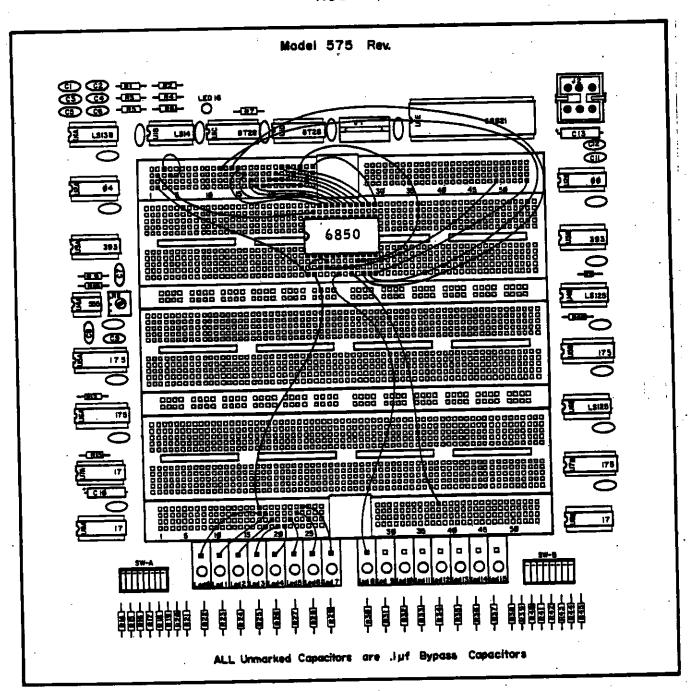

| 3 a | 5              | CA-24 (575) board schematic                                      |  |  |

| 3b  | 6              | CA-24 (575) board schematic                                      |  |  |

| 4   | 9              | CA-24 (575) board power connection and distribution              |  |  |

| 5   | 12             | Logic "1" (+5 Volts) connected to LEDØ                           |  |  |

| 6   | 13             | Logic "Ø" (Ø Volts) connected to LEDØ                            |  |  |

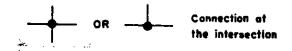

| 7   | 16             | SW1A connected to LEDØ                                           |  |  |

| 8   | 18             | Clock signals connected to LED's                                 |  |  |

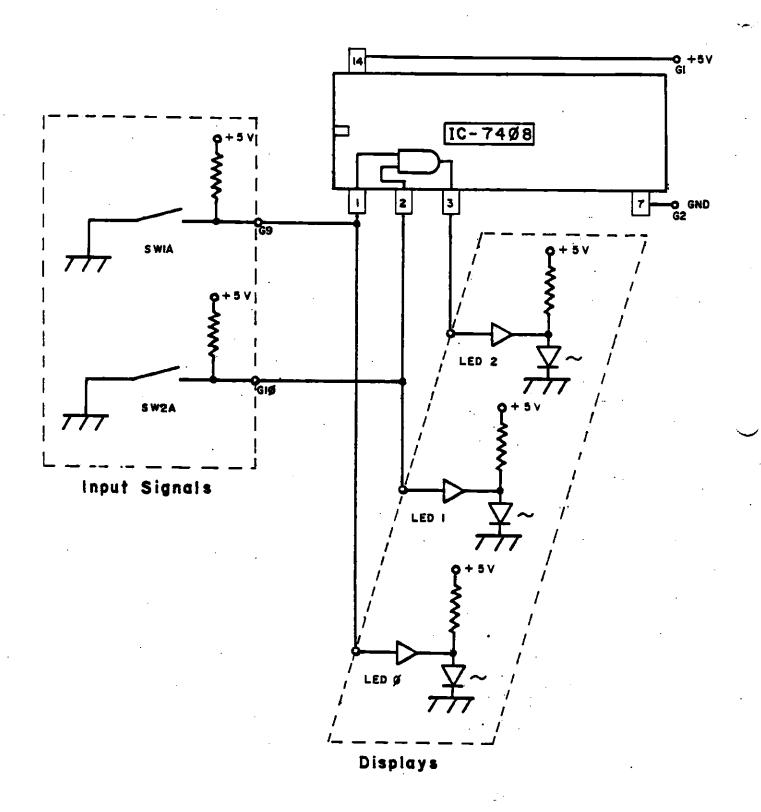

| 9   | 24             | Switch and LED connections to an AND gate                        |  |  |

| 10  | 25             | Schematic for AND gate circuit                                   |  |  |

| 11  | 30             | Schematic for NAND gate circuit                                  |  |  |

| 12  | 31             | Switch and LED connections to a NAND gate                        |  |  |

| 13  | 33             | Schematic for a NAND gate used as an inverter                    |  |  |

| 14  | 34             | Switch and LED connections to a NAND gate inverter               |  |  |

| 15  | 37             | Schematic for NOR gate circuit                                   |  |  |

| 16  | 38             | Switch and LED connections to a NOR gate                         |  |  |

| 17  | 39             | Schematic for a NOR gate used as an inverter                     |  |  |

| 18  | 40             | Switch and LED connections to a NOR gate inverter                |  |  |

| 19  | 43             | Schematic for an OR gate made from NOR gates                     |  |  |

| 20  | 44             | Switch and LED connection to OR gate                             |  |  |

| 21  | 47             | Switch, LED, and inter-chip connections for an exclusive OR gate |  |  |

| 22   | 48 | Schematic for an exclusive OR gate made from AND, NAND, and NOR gates                               |

|------|----|-----------------------------------------------------------------------------------------------------|

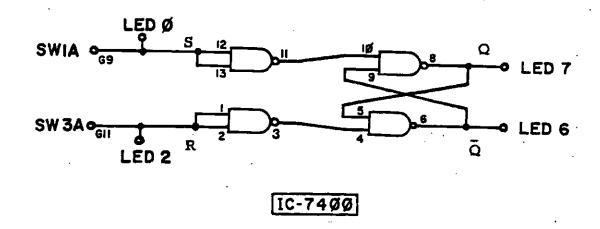

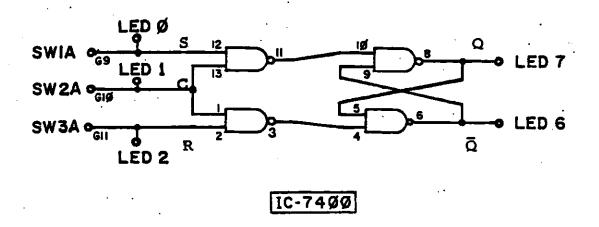

| 23a  | 51 | Schematic for an R-S flip-flop made from NAND gates                                                 |

| 23b  | 51 | Schematic for an R-S flip-flop with clock input                                                     |

| 24   | 52 | Switch, LED, and other connections for an R-S flip-flop                                             |

| 25   | 55 | Switch, LED, and other connections for an R-S flip-flop with clock input                            |

| 26   | 56 | Connection for use of the on-board clock with the R-S flip-flop                                     |

| 27   | 59 | Switch and LED connections to a D flip-flop                                                         |

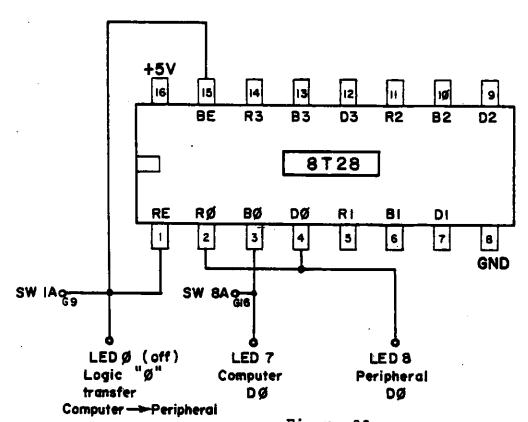

| 28   | 63 | Switch and LED connections to a three-<br>state bus transceiver: computer to peripheral<br>transfer |

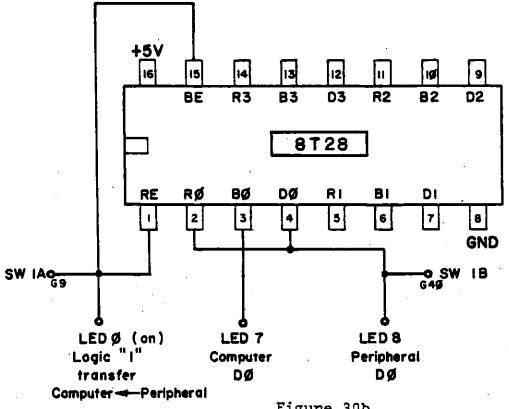

| 29   | 64 | Switch and LED connections to a three-<br>state bus transceiver: peripheral to computer<br>transfer |

| 3Øa  | 65 | Schematic for computer to peripheral transfer across a three-state bus transceiver                  |

| 3 Øb | 65 | Schematic for peripheral to computer transfer across a three-state bus transceiver                  |

| 31   | 70 | Connections for use of LED's to count contact bounce                                                |

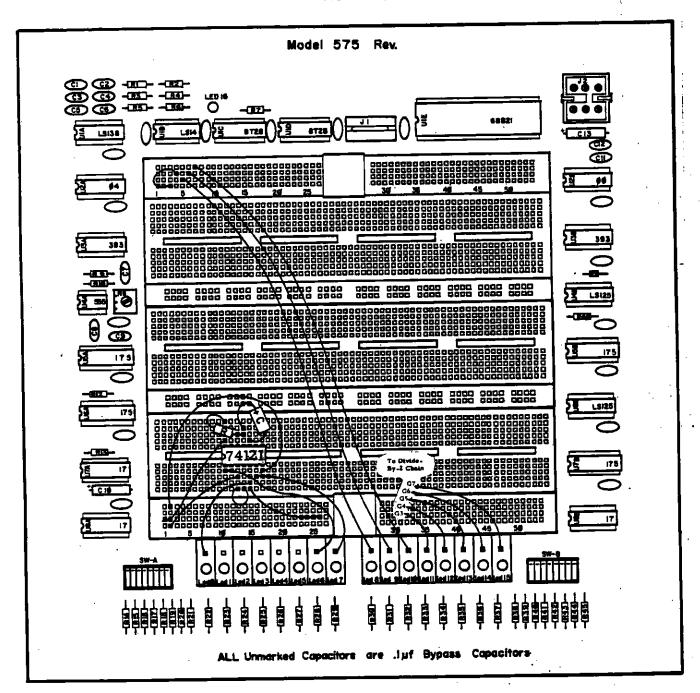

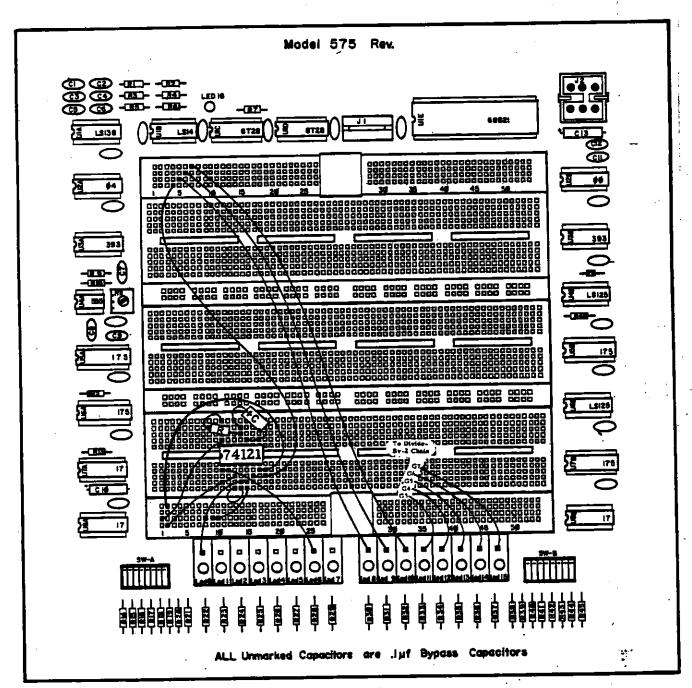

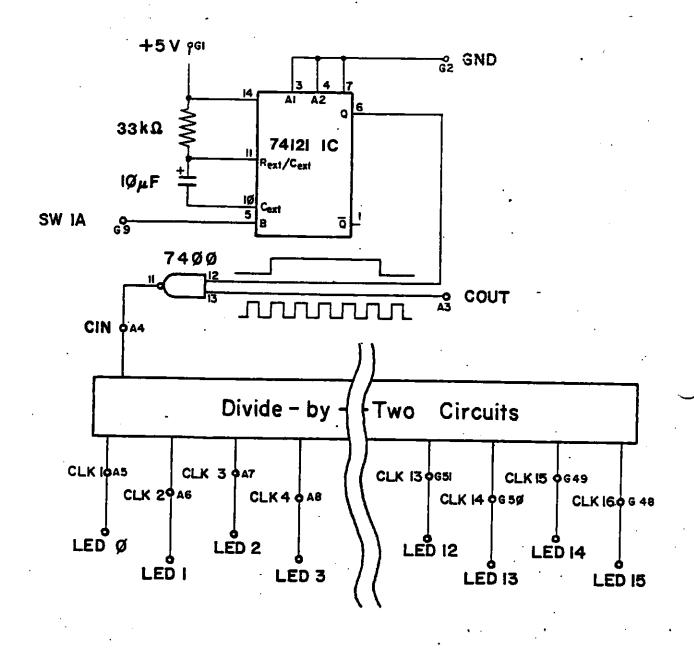

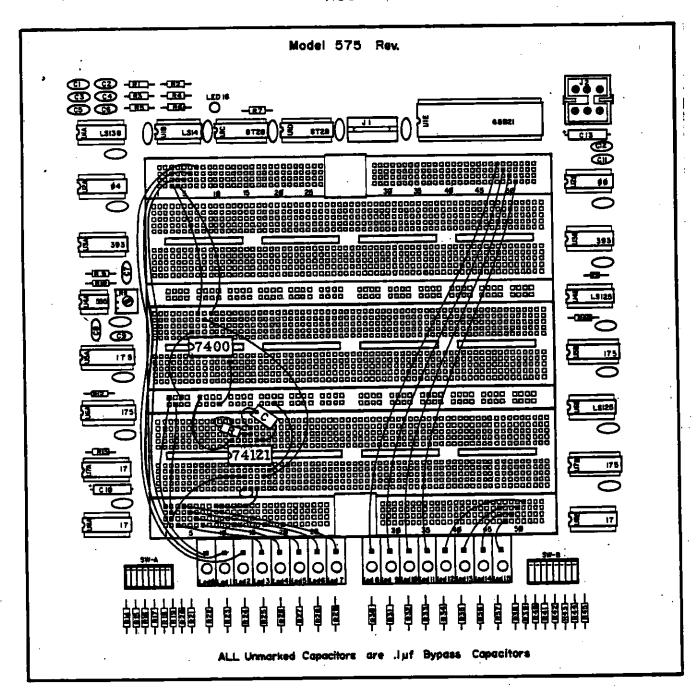

| 32   | 72 | Connections for use of SW1A with a Ø.2 sec monostable multivibrator                                 |

| 33   | 74 | Connections for use of clock signal with a 0.2 sec monostable multivibrator                         |

| 34   | 75 | Connections for use of SWIA and the monostable multivibrator to advance the counting circuit        |

| 35   | 76 | Schematic for timing the monostable multivibrator pulse width                                       |

| 36   | 77 | Connections for circuit used to time the monostable multivibrator pulse width                       |

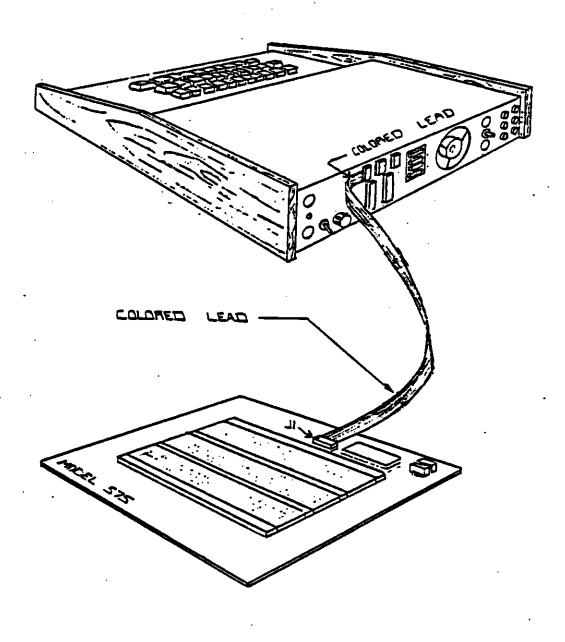

| 37   | 83 | Connection of CA-24 board to C4PMF or C4PDF computer                                                |

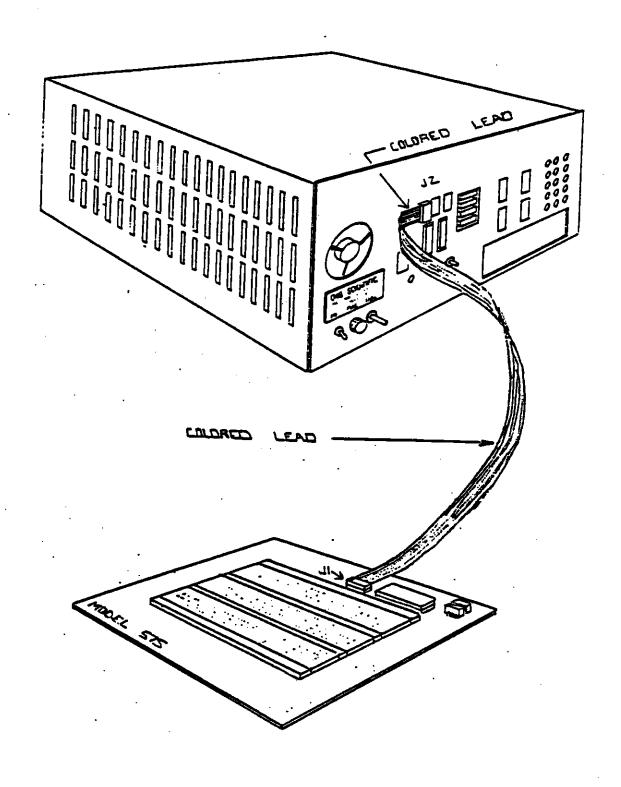

| 38 | 84  | Connection of CA-24 board to C8PDF computer                                                |

|----|-----|--------------------------------------------------------------------------------------------|

| 39 | 89  | Connections for latch output to LED's                                                      |

| 40 | 95  | Connections for switch level entry by way of on-board latches (latch output is also shown) |

| 41 | 101 | Connections for PIA input and output                                                       |

| 42 | 108 | Connection for use of additional PIA                                                       |

| 43 | 111 | Connections for switch simulation of weathervane positions (PIA interfacing)               |

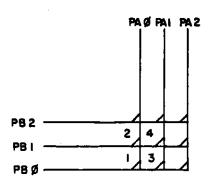

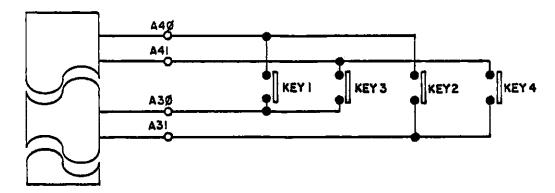

| 44 | 115 | Connections for switch simulation of four keys of a key board (PIA interfacing)            |

| 45 | 125 | Connections for producing a clock pulse to simulate a single photogate interrupt signal    |

| 46 | 127 | Connections for use of SW1B and SW8B to simulate interrupt signals from two photogates     |

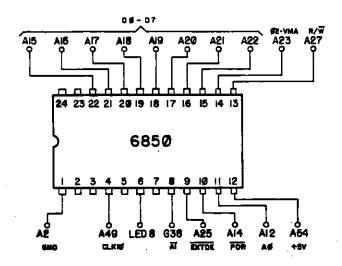

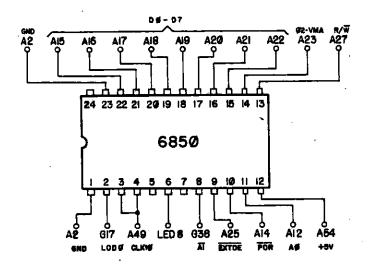

| 47 | 134 | Connections for ACIA serial output to LED8 (approximate Baud rate of 1)                    |

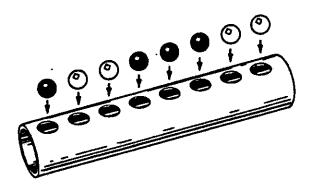

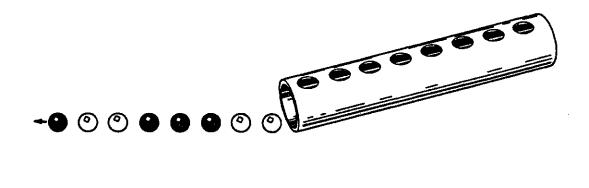

| 48 | 137 | Serial patterns (bit sequences) for various control register settings and data numbers     |

| 49 | 138 | Connections for serial input to the ACIA (approximate Baud rate of 1)                      |

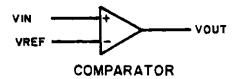

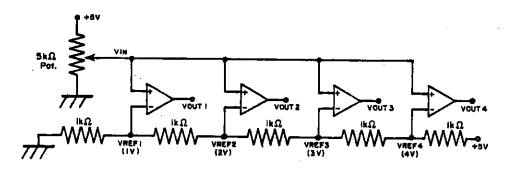

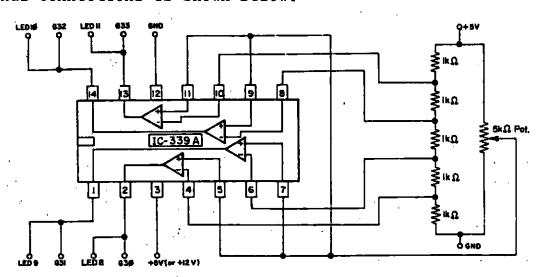

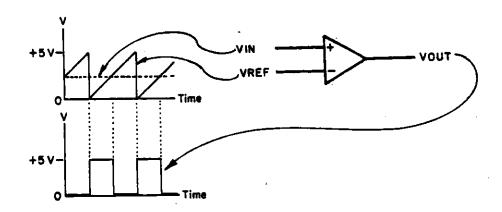

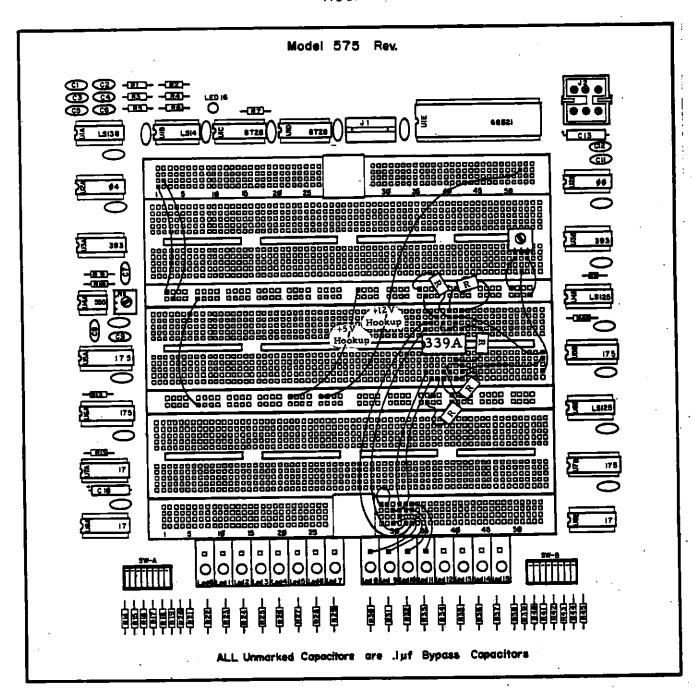

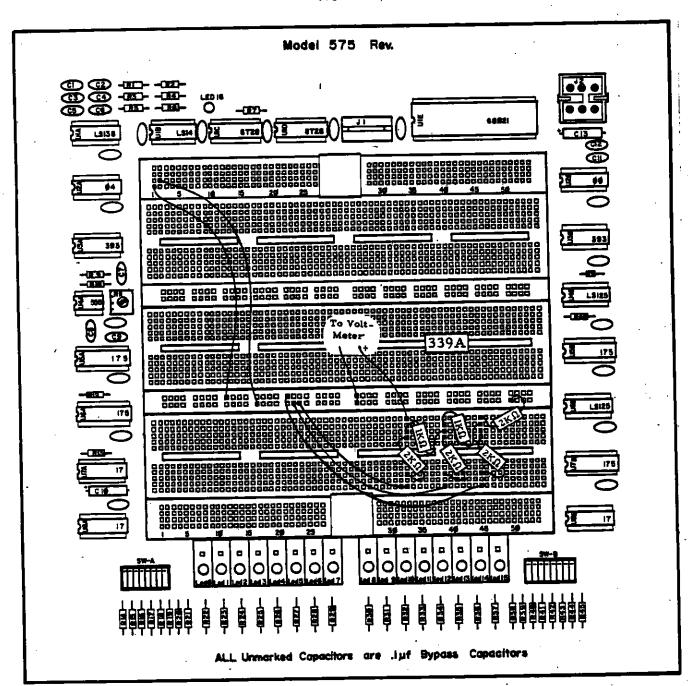

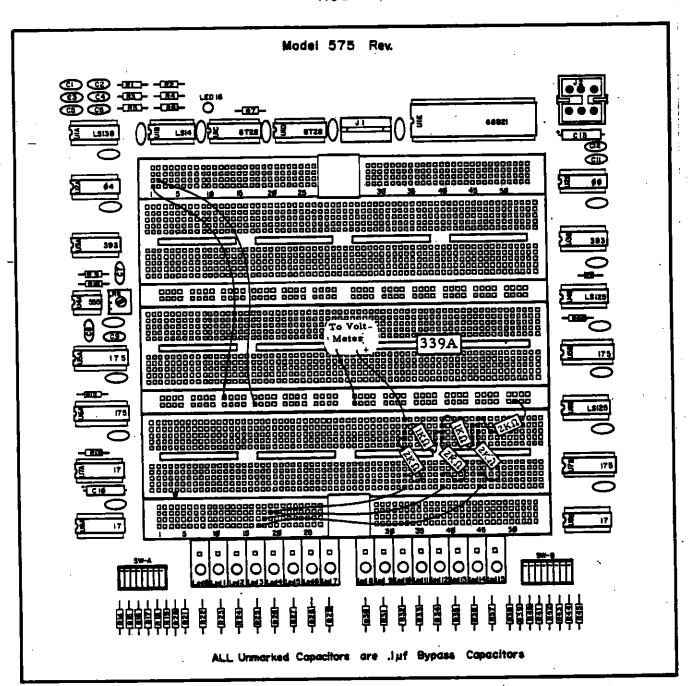

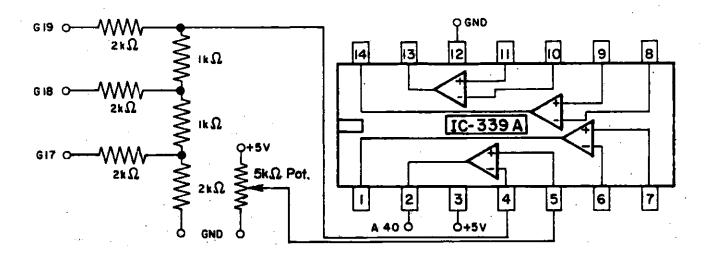

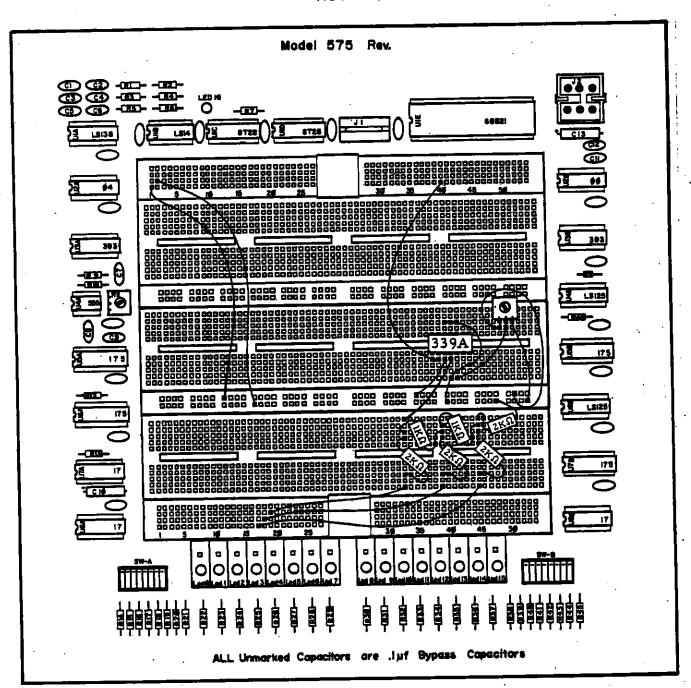

| 50 | 146 | Connections for constructing a very low resolution analog to digital converter             |

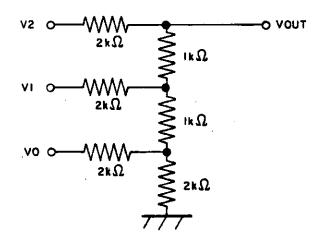

| 51 | 151 | Connections for a three input resistor ladder network                                      |

| 52 | 153 | Connections for latch generated levels for input to the resistor ladder network            |

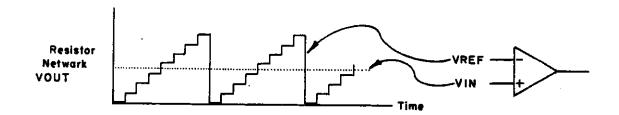

| 53 | 155 | Connections for combined digital to analog conversion and analog to digital conversion     |

#### SECTION I

# DESCRIPTION AND USES OF THE CA-24 EXPERIMENTER'S BOARD

# STAND ALONE BREADBOARD

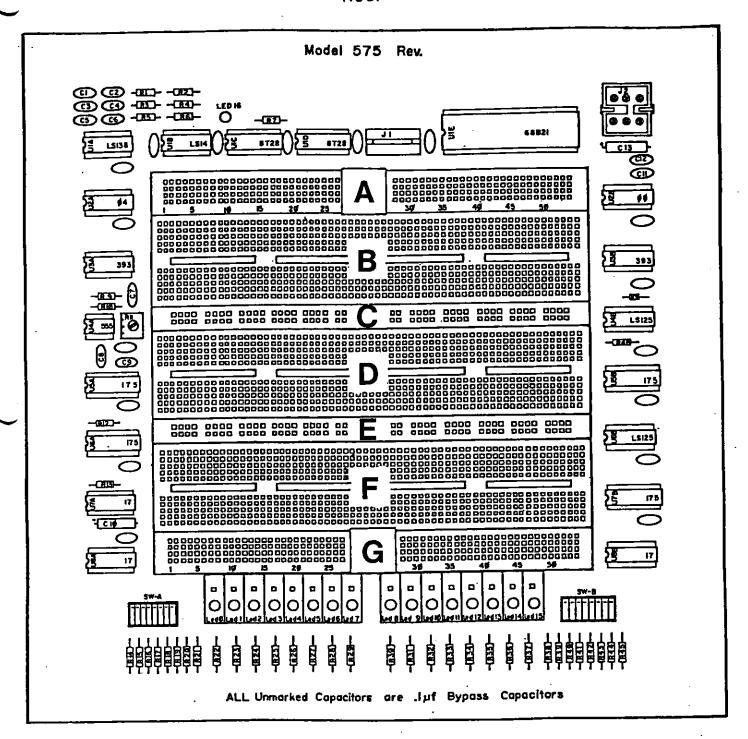

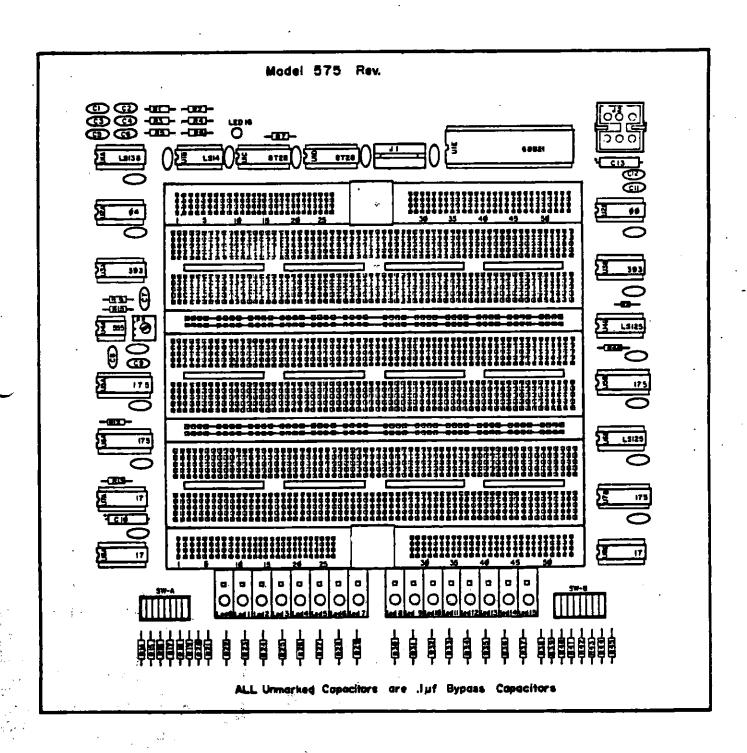

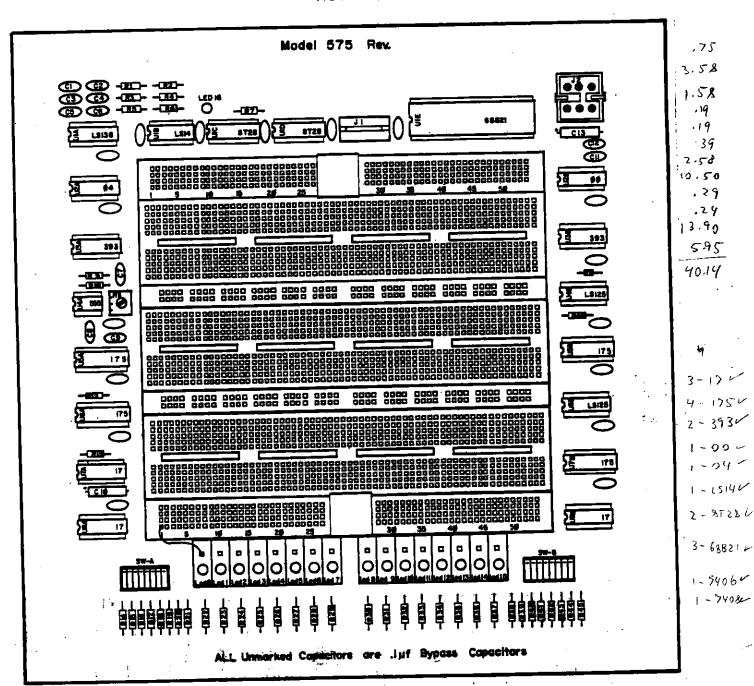

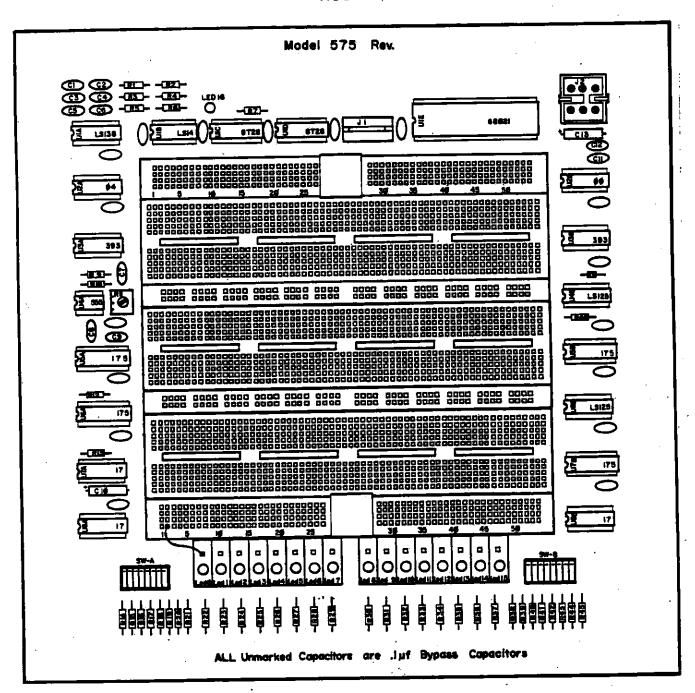

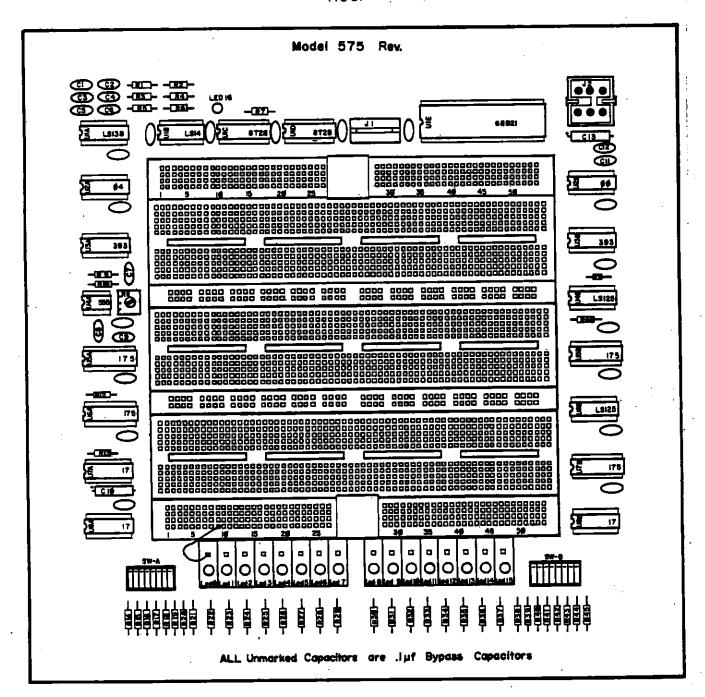

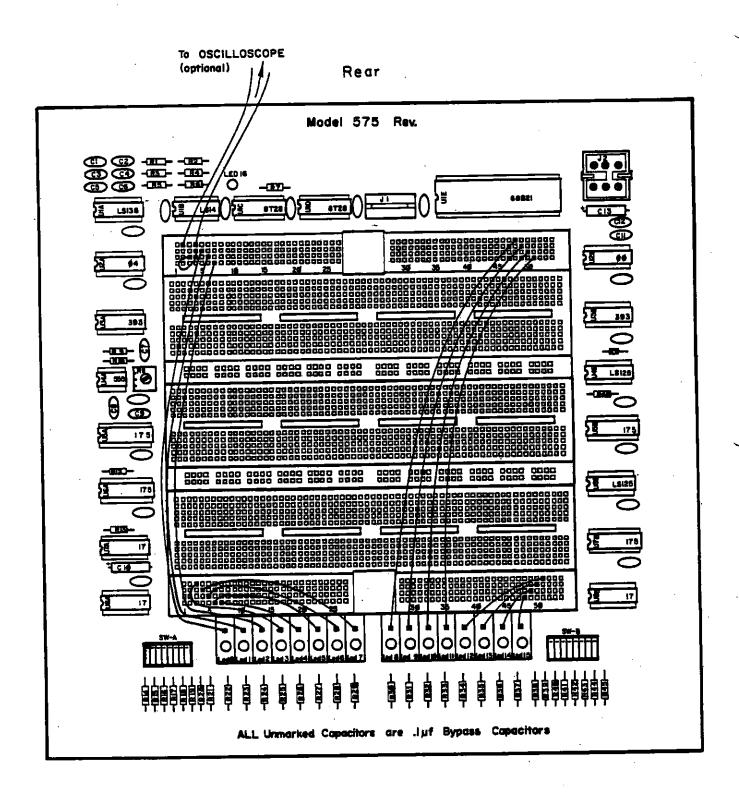

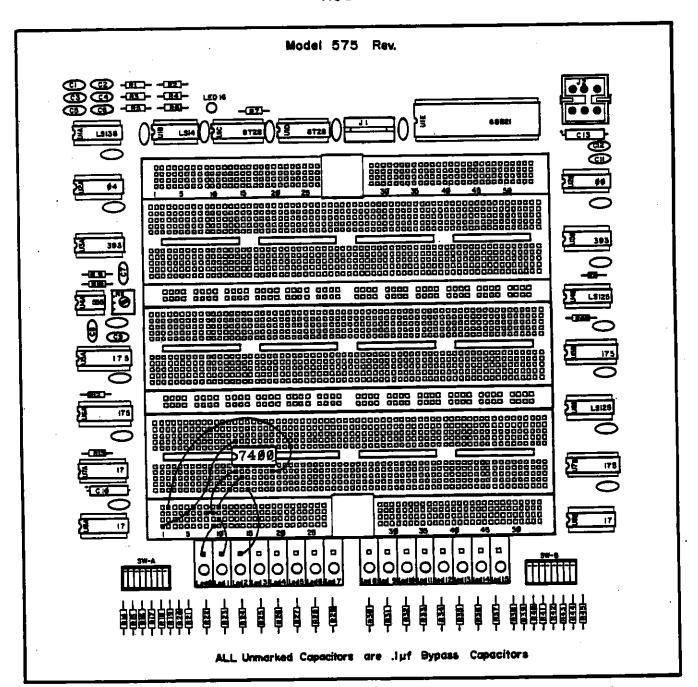

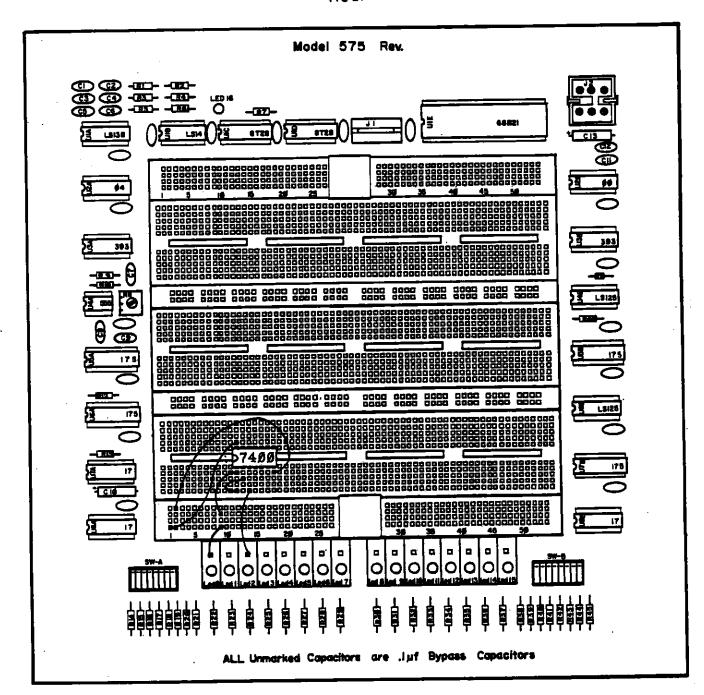

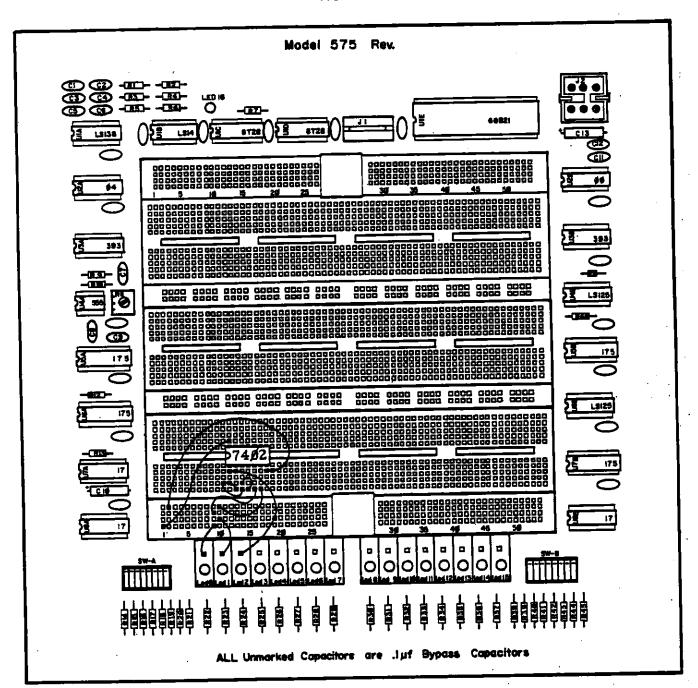

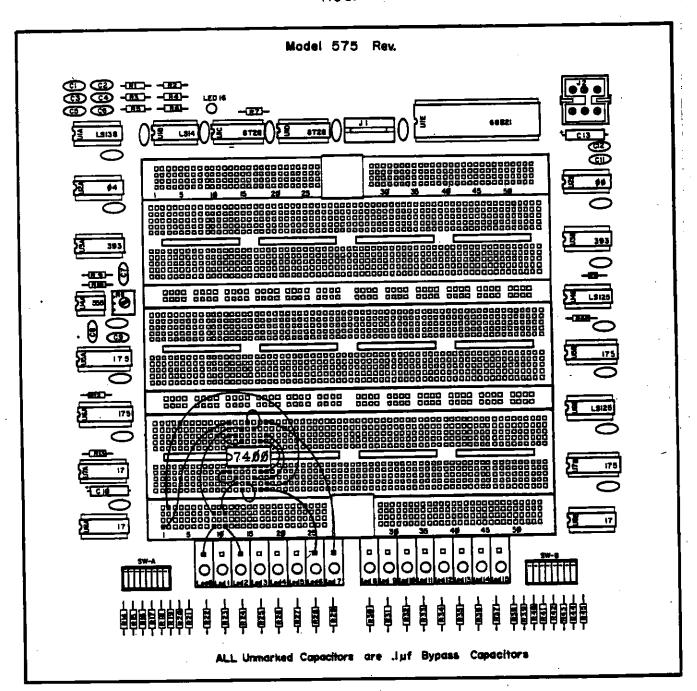

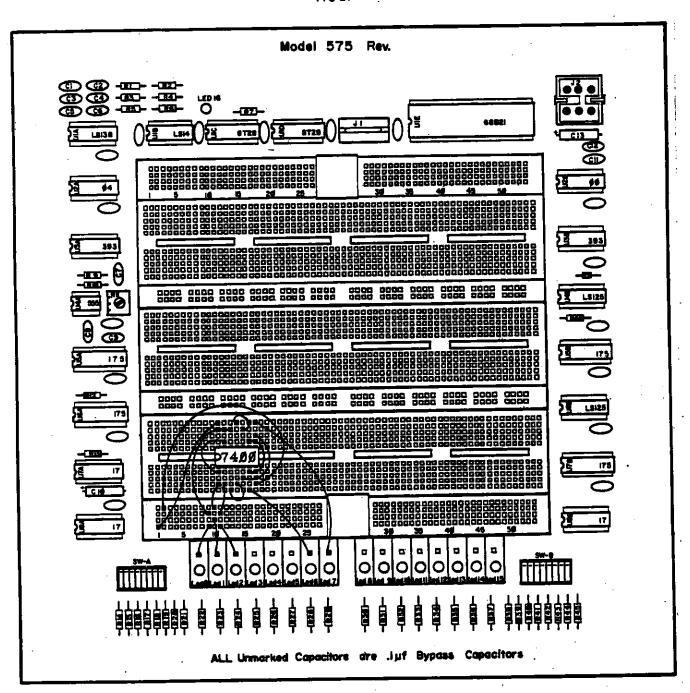

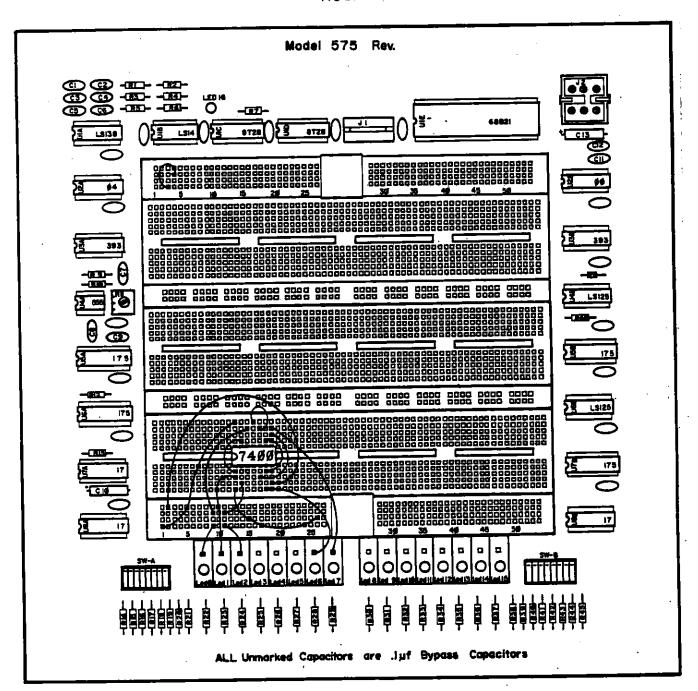

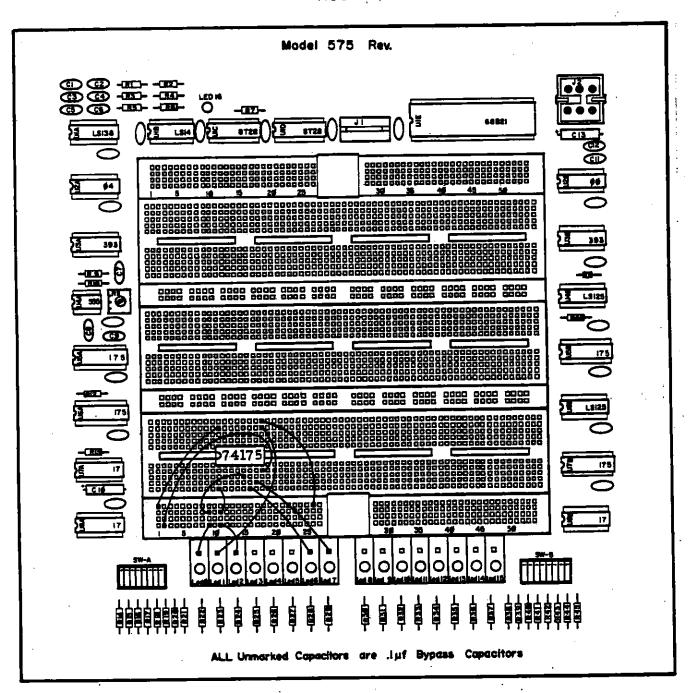

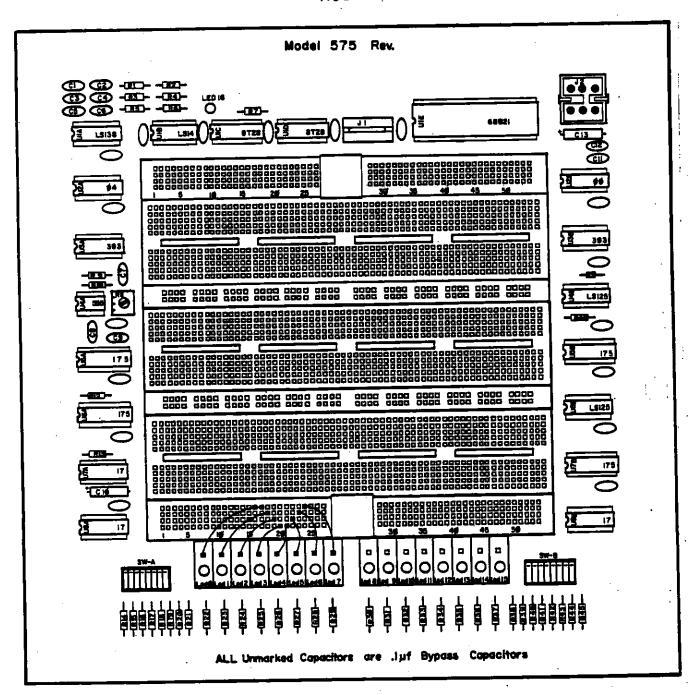

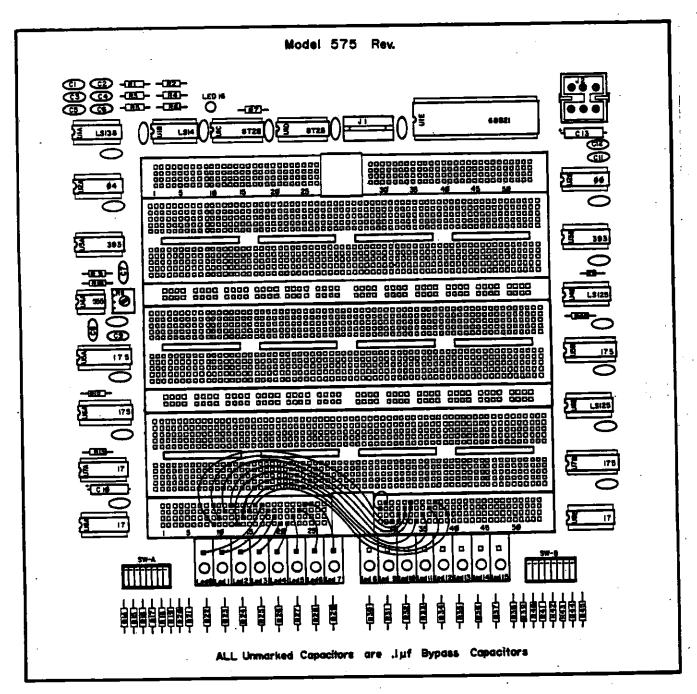

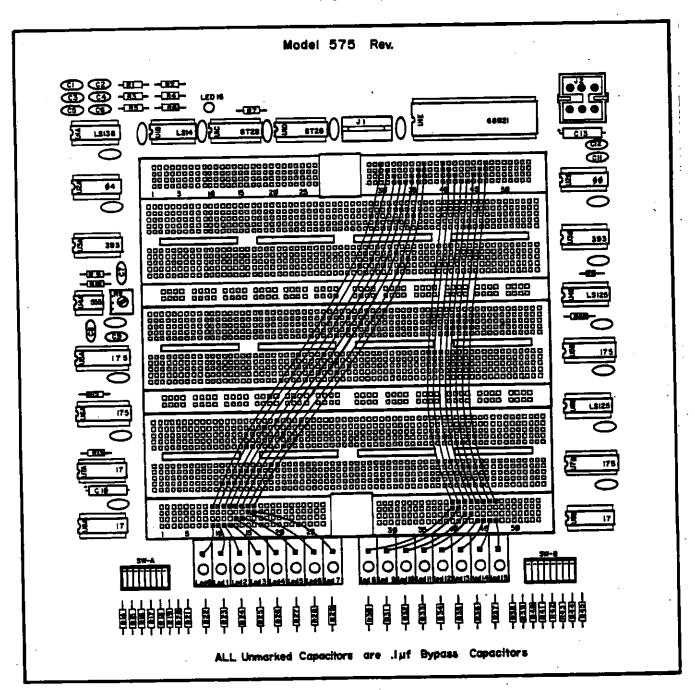

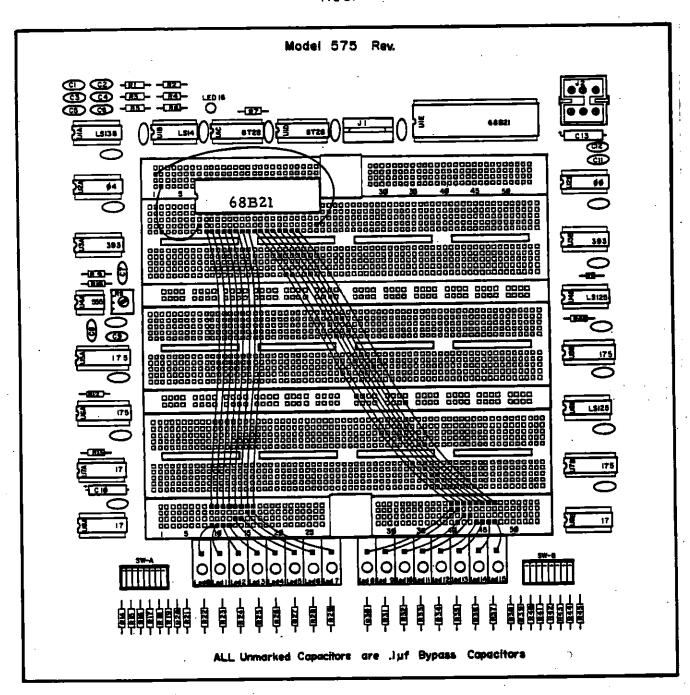

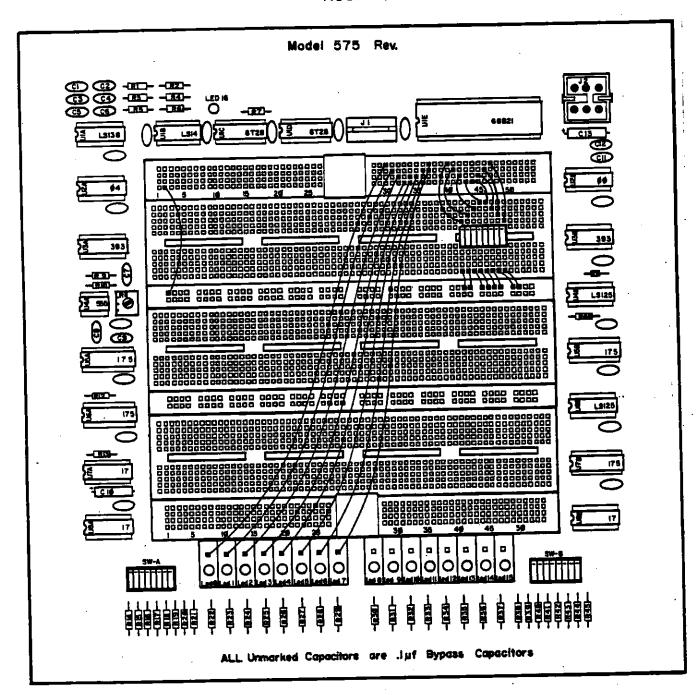

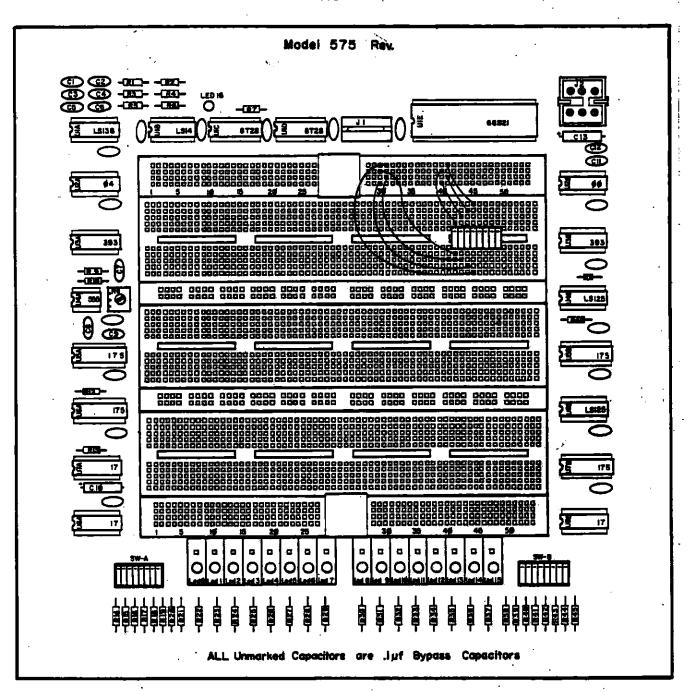

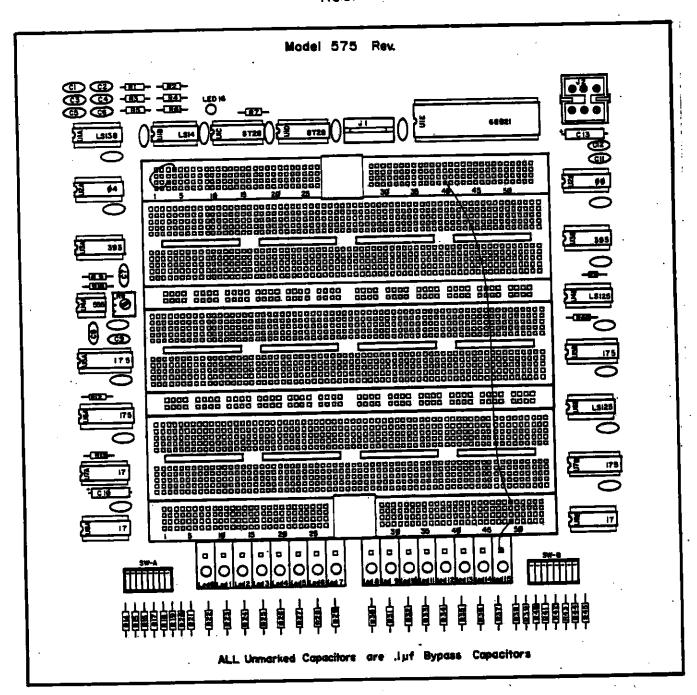

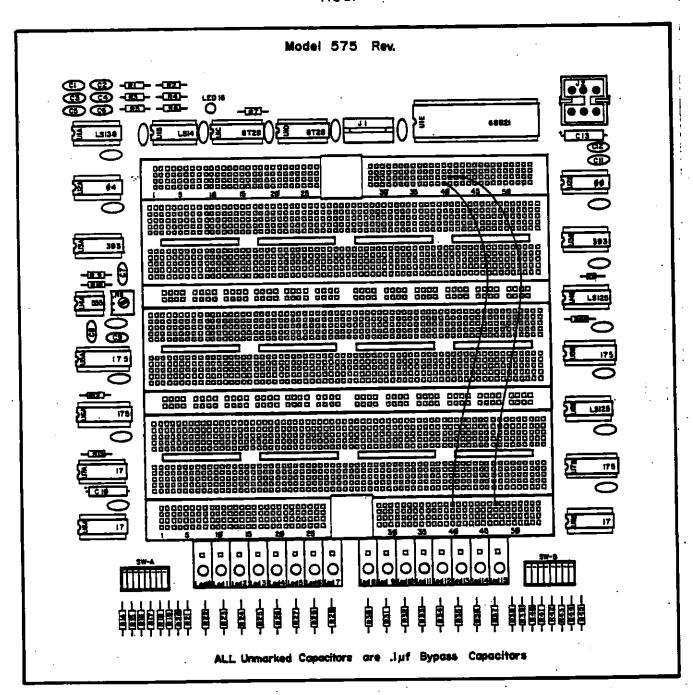

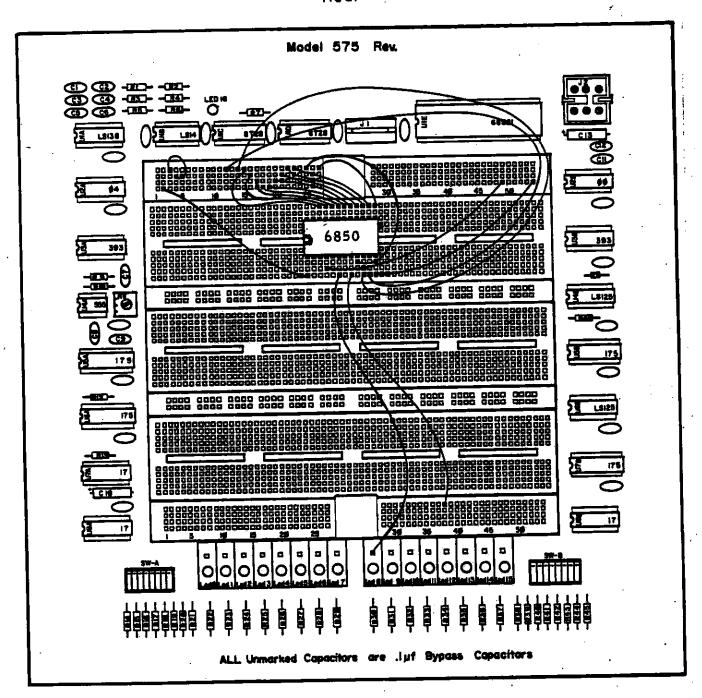

The CA-24 experimenter's board is a versatile device which includes active circuitry and a large breadboard area on which both digital and analog circuits can be constructed. The physical layout of the board is shown in Fig. 1 while Fig. 2 shows the connections between terminals on the under side of the breadboard area (strips A through G).

Terminal strips B, D, and F are intended for integrated circuit use. Each side of the strip, separated by the mid-strip indentation, consists of 5 interconnected terminals. There are 64 sets of these 5 interconnections on each side of the strip.

Strips C and E are used for power distribution. Each strip consists of terminals connected to 2 single conductors which run the length of the strip.

Terminals for signals from and to the active circuit elements are on strips A and G. Power for components which you will place on the breadboard is also available at these strips. Connections to the terminals should be made with single strand wire in the size range of AWG 20 to AWG 26. Wire size smaller then AWG 26 may not make good contact, and wire which is too large in diameter may damage the terminal housing. The recommended size is AWG 22.

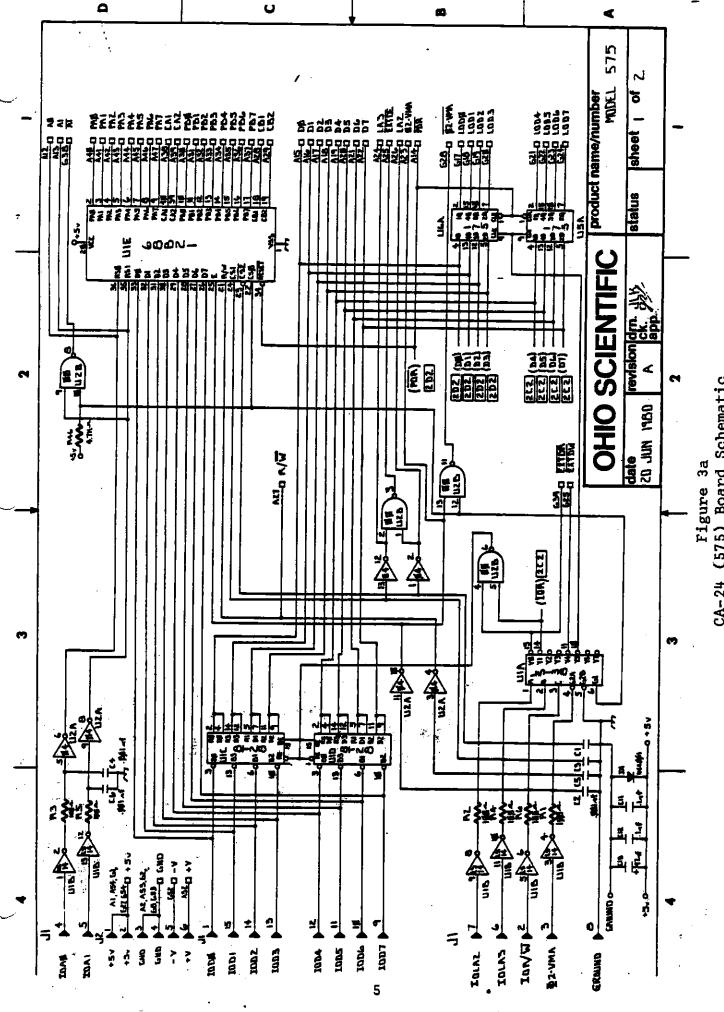

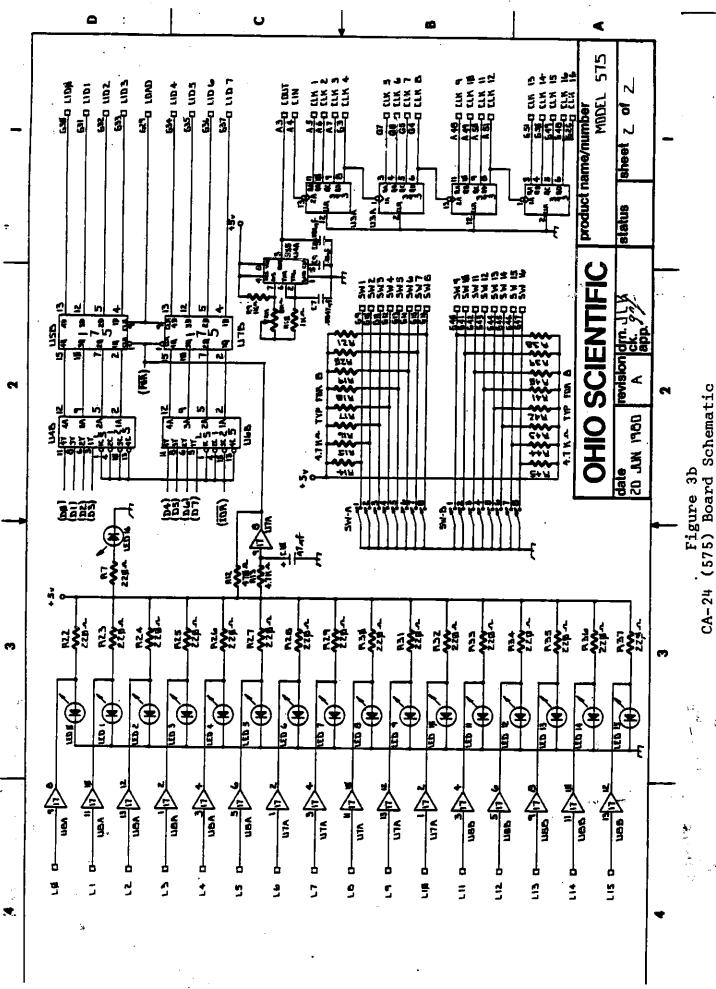

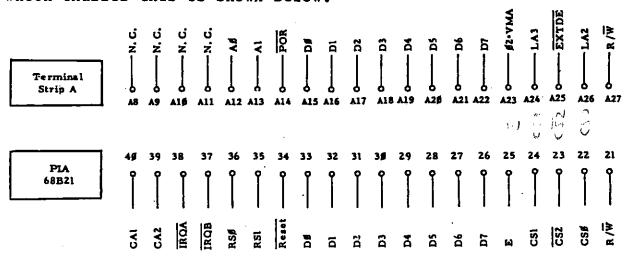

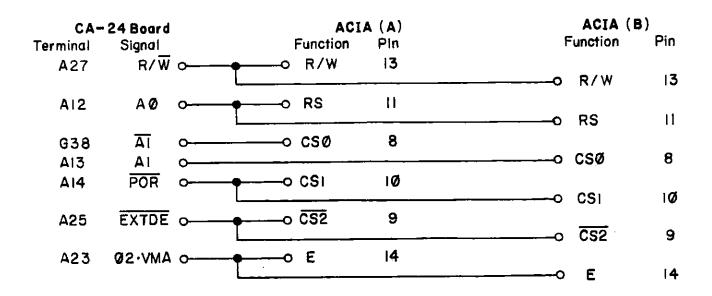

The list of signals corresponding to the terminals on strips A and G is given in Table 1 and the schematic diagrams for the active circuit components are shown in Fig. 3a and 3b. On the far right of these diagrams are also the signal labels found in Table 1. Extra copies of Table 1 and Figures 3a and 3b have been included in Appendix 3. It will be helpful to remove these diagrams for easy reference as you work through the experiments in this manual.

When digital circuits are tested, logic levels (Ø V and +5 V) need to be available for input signals. Throughout this manual Ø V will be referred to as logic "Ø" or "FALSE" and +5 V will be referred to as logic "l" or "TRUE". These levels can be produced either by the set of 16 switches located at the left and right front of the board (SW-A and SW-B), or by a series of clock pulses generated by a 555 IC chip (left side of the board).

In addition to the clock whose frequency can be varied from 25 kHz to 70 kHz, a series of 16 divide-by-two circuits form a frequency reduction chain through which the base frequency of the clock can be reduced by factors of 2 raised to powers ranging from 1 to 16. The combination of the variable frequency clock and the divide-by-two chain allow for a continuous range of clock pulse rates from 0.4 Hz to 70 kHz.

Front

Figure 1

Terminal Strip Labeling

Figure 2 Under-Side Terminal Connections

TABLE 1 CA-24 On Board Terminal Strip Connections

| Terminal | STRIP(G)          | Terminal | STRIP(A)            |

|----------|-------------------|----------|---------------------|

| G1       | VCC /15 V)        | A1       | 1700 (LE 11)        |

| G2       | VCC (+5 V)<br>GND | A1<br>A2 | VCC (+5 V) GND      |

| G2<br>G3 | CLK4              | A2<br>A3 | COUT                |

| G 4      | CLK8              | A3<br>A4 |                     |

| G5       | CLK7              | A5       | CIN<br>CLK1         |

| G6       | CLK6              | A6       | CLK1                |

| G7       | CLK5              | A7       | CLK2                |

| G8       | GND               | A8       | N.C.                |

| G9       | SW1A              | A9       | N.C.                |

| G1Ø      | SW2A              | A1Ø      | N.C.                |

| G11      | SW3A              | A11      | N.C.                |

| G12      | SW4A              | A12      | AØ                  |

| G13      | SW5A              | A13      | Al                  |

| G14      | SW6 A             | A14      | POR                 |

| G15 .    | SW7A              | A15      | DØ                  |

| G16      | SW8 A             | A16      | D1                  |

| G17      | LODØ              | A17      | D2                  |

| G18      | LOD1              | A18      | D3                  |

| G19      | LOD2              | A19      | D4                  |

| G 2Ø     | LOD3              | A2Ø      | D5                  |

| G21      | LOD4              | A21      | D6                  |

| G22      | LOD5              | A22      | D7                  |

| G 23     | LOD6              | A23      | Φ 2 • VMA           |

| G 24     | LOD7              | A24      | LA3                 |

| G 25     | EXTDW             | A25      | EXTDE               |

| G 26     | CLK16             | A26      | LA2                 |

| G 27     | VCC               | A27      | R/₩                 |

| G 28     | <b>§2·VMA</b>     | A28      | CB1                 |

| G 29     | LOAD              | A29      | CB2                 |

| G3Ø ·    | LIDØ              | A3Ø      | PBØ                 |

| G31      | LID1              | A31      | PB1                 |

| G32      | LID2              | A3 2     | PB2                 |

| G33      | LID3              | A33      | PB3                 |

| G34      | LID4              | A34      | PB4                 |

| G35      | LID5              | A35      | PB5                 |

| G36      | LID6              | A36      | PB6                 |

| G37      | <u>LI</u> D7      | A37      | PB7                 |

| G38      | <u>ĀĪ</u>         | A38      | CA1                 |

| G39      | EXTOR             | A39      | CA2                 |

| G4Ø      | SW1B              | A4Ø      | PAØ                 |

| G41      | SW2B              | A41      | PA1                 |

| G42      | SW3B              | A42      | PA2                 |

| G43      | SW4B              | A43      | PA3                 |

| G44      | SW5B              | A44      | PA4                 |

| G 45     | SW6B              | A45      | PA5                 |

| G 46     | SW7B              | A46      | PA6                 |

| G47      | SW8 B             | A47      | PA7                 |

| G 48     | CLK16             | A48      | CLK9                |

| G 49     | CLK15             | A49      | CLK1Ø               |

| G5Ø      | CLK14             | A5Ø      | CLK11               |

| G51      | CLK13             | A51      | CLK12               |

| G52      | -V (-12 V or -15  |          | +V (+12 V or +15 V) |

| G53      | GND               | A53      | GND                 |

| G54      | VCC (+5 V)        | A5 4     | VCC (+5 V)          |

CA-24 (575) Board Schematic

, 600 600.

6

For digital circuits, it is frequently necessary to display logic levels both for input signals and for output signals. There are 16 light emitting diodes (LED's) for this purpose mounted at the front of the board. In Fig. 1, they are marked LEDØ through LED15.

If analog circuits are constructed on the board, they can be powered from terminals on strips A and G (provided that the proper power supply has been connected to the board). Varying voltage input signals, however, need to be generated by some device external to the board, and the display of the input and output signals must be done on instruments external to the board.

The CA-24 experimenter's board used as a stand-alone device is an excellent tool for the hobbyist or for the person working in electronic circuit design. On it, trial circuits can easily be constructed and evaluated. Furthermore, the board is an excellent teaching device. Experiments in this manual form a nucleus of material by which a person can learn about digital circuit performance. In addition, an educator can design experiments which suit the purposes of a course which includes basic electronic circuitry.

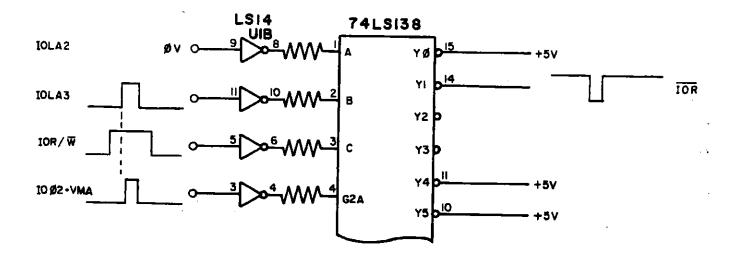

## COMPUTER INTERFACED BREADBOARD

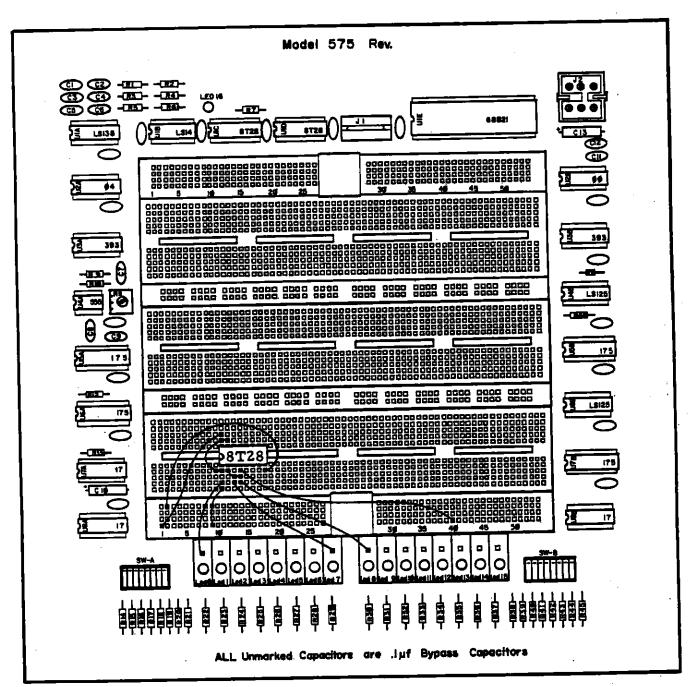

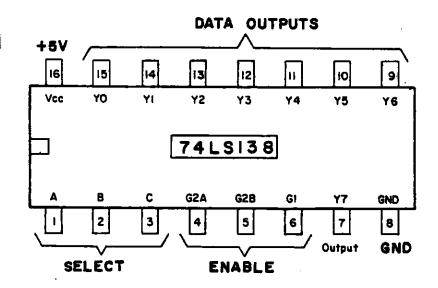

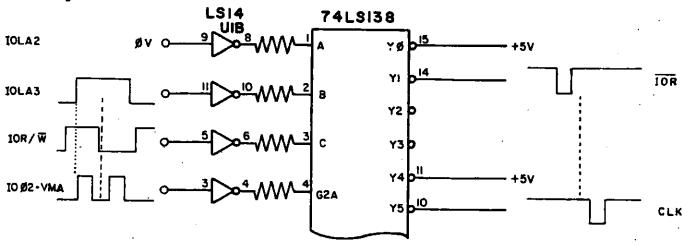

More advanced circuits can take advantage of the computer interface circuity which resides on the CA-24 experimenter's board. The interface components include a 3-to-8 line decoder/multiplexer for processing control signals, bi-directional latches (or bus transceivers) for transferring information back and forth between the CA-24 board and a computer, TTL (Transistor-Transistor Logic) latches for transferring signals back and forth between the board and external devices, and a PIA (Peripheral Interface Adapter) which permits a computer to have a broad range of control over peripheral devices.

The interfacing feature of the CA-24 board will also be useful for the hobbyist, the person working in circuit design, and the educator. Additional interfacing components can be added to the breadboard and circuits built around them evaluated. The experiments in the latter portion of the manual introduce the user to interfacing techniques and give some practical examples.

We expect you will find your CA-24 board to be an interesting and worthwhile investment.

# SECTION II

# EXPERIMENTS USING ONLY THE CA-24 BOARD AND POWER SUPPLY

# OVERVIEW AND POWER SUPPLY CONNECTION

The following twelve experiments can be worked through using only the CA-24 board (with power supply attached) and the components selected from those supplied with the board. The experiments are designed to familiarize you with with the basic functions of the board and with some relevant digital electronic circuits. Experiments 10, 11, and 12 (particularly 10 and 11) will help you to understand the function of IC chips on the board which allow it to interact with a computer.

For the most part, the experiments are in order of increasing complexity. If you have some familiarity with digital electronics and integrated circuits, you may wish to work through Experiments 1, 2, and 3 and then jump ahead to the point where you feel the experiments would be of value.

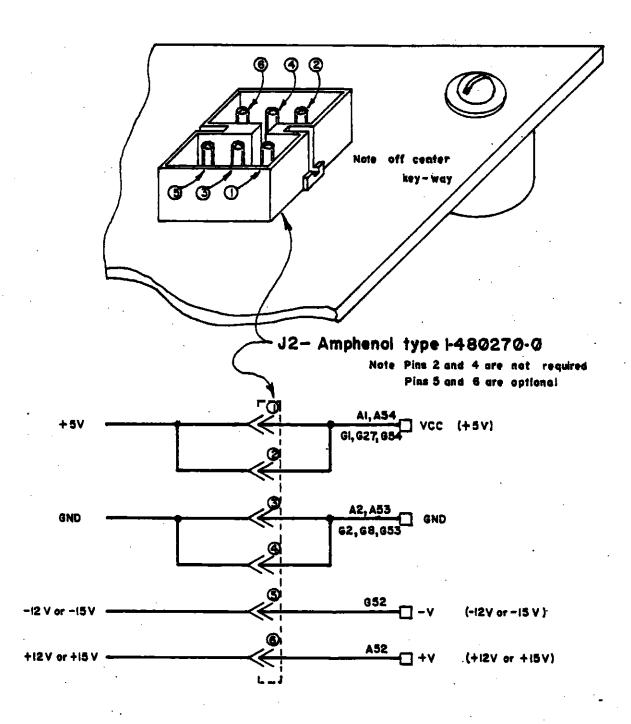

In order to use the CA-24 board, it is necessary to connect a power supply to the board. This is done by way of connector J2 in the rear right corner of the board (Amphenol type 1-480270-0 with pins type 60619-1). The pin connections are shown in Fig. 4. Be certain that the power supply is off when the connection is made.

The voltage which is necessary for the operation of the digital circuit components mounted on the board is +5 V. All of the permanent circuit components of the board are powered by this voltage. In order to have sufficient current capability to meet the requirements of components used in various experiments throughout the manual, the power supply must be able to deliver about 1 Ampere.

If you should have occasion to use the breadboard area for constructing analog circuits, you will need also the +12~V (or +15~V) and the -12~V (or -15~V) power. Current requirements probably would not be greater than 100~mA. These voltages, however, are not necessary for the experiments which follow.

When you are certain that the appropriate power supply has been correctly connected to the CA-24 board, proceed to Experiment 1.

# CA-24 POWER CONNECTION and DISTRIBUTION

Figure 4 CA-24 (575) Board Power Connection and Distribution

TITLE

LED Indicators

## **PURPOSE**

The purpose of this experiment is to investigate the function of the seventeen LED (light emitting diode) indicators on the CA-24 board.

# EQUIPMENT

CA-24 board and power supply One short (about 2 inch) jumper wire (22 gauge)

# **DISCUSSION**

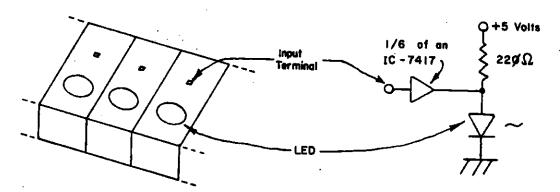

The light emitting diode (LED) is an inexpensive indicator or display device. On the CA-24 board, a single LED functions as a "power-on" indicator. It is located at the rear (power cable end) of the board and is marked LED16 in Fig. 5. Sixteen additional LED's are in two groups of eight at the front of the board and are marked LEDØ through LED15 in Fig. 5. These sixteen additional indicators are pre-wired as shown below.

Shown also is a sketch of three LED housings. Each 220 resistor is located in front of the LED to which it is wired. The resistors are labeled R22 through R37 on Fig. 5. triangle symbol marked "one-sixth of an IC-7417" represents identity element (same output as input) which acts as a buffer between the LED and a signal connected to it. The identity element is most commonly called a buffer or a driver. There are three 7417 chips on the CA-24 board. They are marked U7A, U8A, Each 7417 chip contains six identity and USB in Fig. 5. elements or buffers.

Each LED will require a maximum current of 20 mA. When all of them are on, the power requirement is 17 times 20 mA or about 1/3 Ampere. This heavy power consumption (relative to

other circuits on the board) should be kept in mind when a power supply for the CA-24 board is being considered and is the principal reason a 1 Ampere supply has been recommended.

#### **PROCEDURE**

Be certain that a 5 Volt power supply of sufficient current capability (about 1 A) has been connected to J2 of the CA-24 board as described earlier in this section. Turn on the power supply. Note that all seventeen LED's will glow. The indicators at the front of the board will be on because a floating input (no connection made to the input) will be equivalent to a +5 Volt signal (commonly referred to as logic "1" or high).

Insert one end of a short jumper wire into the input terminal hole of the LEDØ housing. Insert the other end into terminal Gl (one of the four holes at the far left marked 1 on the G terminal strip). The connection with the jumper wire is shown pictorially in Fig. 5. Reference to the terminal strip connections in Table 1 of SECTION I shows that Gl is +5 V. It will be noted that the LED remains on.

Recall that Appendix 3 contains extra copies of Table 1 and Figures 3a and 3b. It will be helpful to remove these diagrams for easy reference as you work through the experiments in this manual.

Next, shift the jumper wire from G1 to G2 as shown in Fig. 6. Table 1 shows that G2 is ground (GND) or Ø Volts. Note that the LED turns off indicating a Ø Volt signal at its input (commonly referred to as logic "Ø" or low).

Can you find other GND or Ø V terminals on strip G? (Refer to Table 1. Do not just start poking the jumper wire into holes.) Try other combinations of LED's and GND terminals on strip G.

Through this experiment you have found that the LED can be used as an indicator for logic levels. When the input to the LED is +5 Volts (called a logic "1" or "true"), the light is on. When the input is Ø Volts (called a logic "Ø" or "false"), the light is off. This simple indicator will serve as the basis for most of our display functions.

# Rear

Front

Figure 5

Logic "1" (+5 Volts) Connected to LEDØ

0ATA 27128 27256

Front

Figure 6

Logic "#" (# Volts) Connected to LED#

# TITLE

Logic Level Switches

# PURPOSE

The purpose of this experiment is to investigate the use of the sixteen switches on the CA-24 board.

# EQUIPMENT

CA-24 board and power supply One short jumper wire

#### DISCUSSION

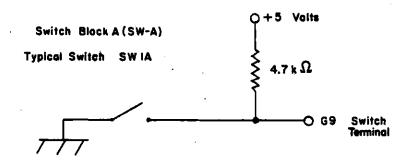

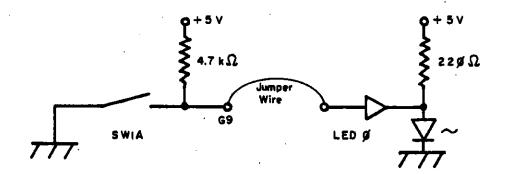

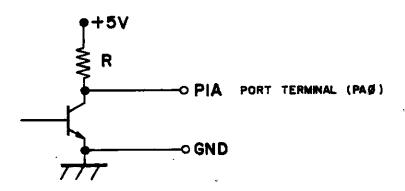

There are 16 single-pole-single-throw (SPST) switches on the CA-24 board (see front left and right corners of Fig. 7) which can be used to set voltage (also called logic) levels. Each switch is pre-wired as shown below for switch 1A (SW1A) in switch block A (SW-A).

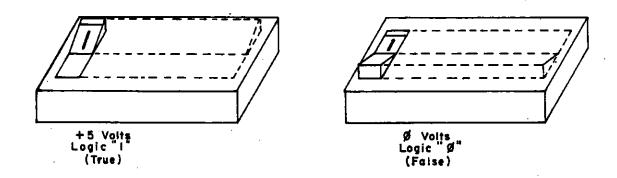

The diagrams below show the switch positions for the two output or logic level conditions.

Note that when the rear end of the switch is up, the switch produces a +5 Volt (logic "1" or "true") signal. When the rear end is down, the switch signal is Ø Volts (logic "0" or

"false"). These signals appear at terminals G9 through G16 for switch block A (the left set) and G40 through G47 for switch block B. (See Table 1 in SECTION I.)

# PROCEDURE

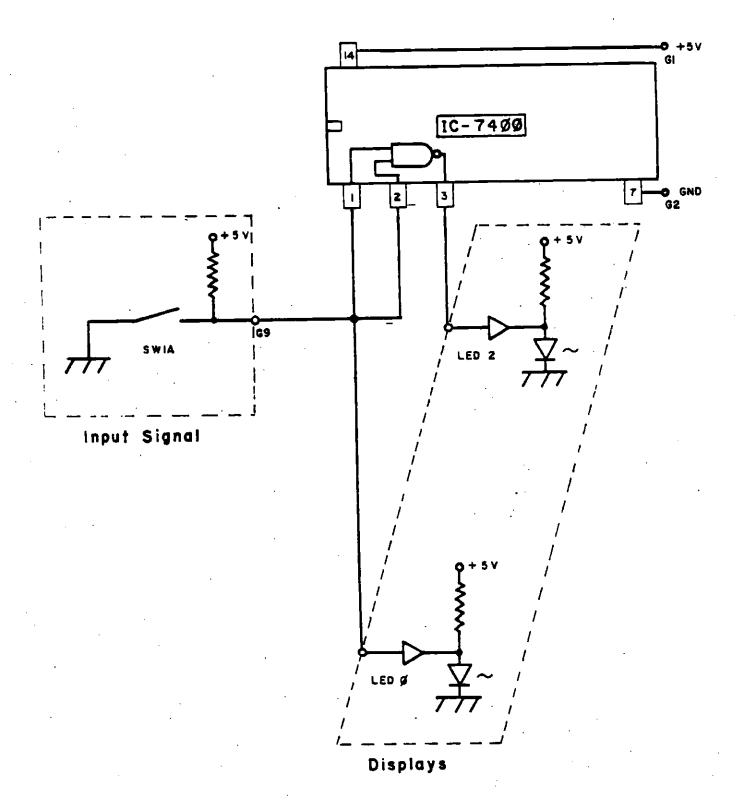

Be certain that the power supply to the CA-24 board is turned off. Connect SWIA to LEDØ as shown schematically below.

This is done by inserting one end of the jumper wire into the terminal hole on the LEDØ housing and the other end into one of the four G9 terminal holes. This connection is pictured in Fig. 7. Now turn on the power supply.

Move the far left switch in switch block A (SW1A) back and forth. Note that LEDØ turns on and off depending on the position of the switch. Now move the jumper wire from G9 to G1Ø. Note that now SW2A controls LEDØ. Try various combinations of switches and LED's to be certain you understand how the switches can be used.

In future experiments we will use switches instead of changing jumper wires to change an input signal. This method will be more convenient and it will allow us to tell at a glance which signals are logic "0" and which are logic "1".

In some circuits, the resistance between the power supply and the switch terminal is important. For those circuits, we must take the internal 4.7 k $\Omega$  resistance into account. We shall point out these critical cases as they arise in future experiments.

Front

Figure 7

SW1A Connected to LEDØ

#### EXPERIMENT 3

TITLE

Adjustable Frequency Clock

# **PURPOSE**

The purpose of this experiment is to investigate the adjustable frequency clock which is a part of the CA-24 board, use it together with the divide-by-two circuits also on the board, and measure its maximum and minimum frequencies.

# EQUIPMENT

CA-24 board with power supply

Six short jumper wires

Four medium jumper wires (about 4 inches)

Seven long jumper wires (about 8 inches)

Screwdriver (narrow tip)

Oscilloscope (optional)

## DISCUSSION

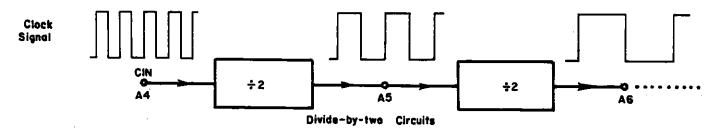

An adjustable square wave oscillator, or clock, producing a series of 0 V to 5 V transitions, is a useful feature of the CA-24 board. This oscillator, together with a group of sixteen divide-by-two circuits provides a wide range of possible signal frequencies. Since the frequency range of the square wave oscillator is adjustable from 25 kHz to 70 kHz and since sixteen divide-by-two circuits will produce an overall division of 65536, the full range of available frequencies is from 70 kHz to about 0.4 Hz. The duty cycle (the fraction of the total time spent at the 5 V level) is approximately 50% except for the highest frequencies directly from the clock which are somewhat greater than 50%.

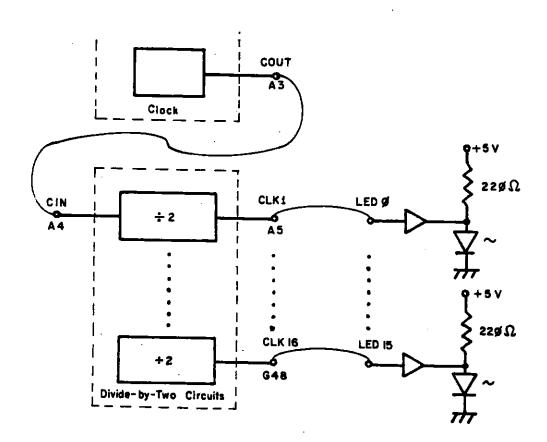

The basic clock signal is produced by an IC chip type 555. The chip is located on the left side of the CA-24 board. It is marked U4A in Fig. 8. The wiring details for this chip are shown in Fig. 3b, slightly right of center. The adjustable resistor R11 varies the frequency of the output signal which is available at terminal A3 (on the strip farthest to the back).

The divide-by-two circuits are in the IC-74393 chips, one on each side of the CA-24 board, toward the rear, labeled U3A and U3B in Fig. 8. Each 74393 chip contains two divide-by-sixteen circuits, each of which is four divide-by-two circuits chained together with outputs after each division. The wiring details in Fig. 3b show how these circuits are strung together. As seen in Table 1 of SECTION 1, the input to the divide sequence is terminal A4 and the outputs after each division are A5 through A7, G3 through G7 (but note the reverse order, G7 through G4, for increasing division), A48 through A51, and a decreasing number sequence of G51 through G48. In addition to the terminal G48, G26 is the location of the lowest

Front

Figure 8

Clock Signals Connected to LED's

frequency output. Note that on the circuit diagram (Fig. 3b) and on the terminal connection list (Table 1) the labels for the output terminals of the divide chain are CLK1 through CLK16. To determine division factor at each output, use the label number as a power of two. For example, terminal A7 is labeled CLK3. Two raised to the third power is eight. A square wave connected to A4, then, will be reduced in frequency by a factor of eight at A7. Since two raised to the sixteenth power is 65536, the frequency of the signal at G48 or G26 is equal to the frequency of the signal at A4 divided by 65536.

#### PROCEDURE

Be certain that the power supply to the CA-24 board is turned off. Use a short jumper wire to connect A3 to A4. Next, connect the outputs of the divide chain to the LED indicators. While any sufficiently long jumper wires can be used to do this, one possibility is to use three long wires to connect A5 to LEDØ, A6 to LED1 and A7 to LED2. Then one short wire will reach from G3 to LED3 while four medium length wires can be used for G7 to LED4, G6 to LED5, G5 to LED6, and G4 to LED7. Now four long wires are needed to connect A48 through A51 to LED8 through LED11. Finally, the last four LED's can be connected to G51 through G48 with short jumper wires. A schematic representation of these connections is shown below.

A picture of these connections is given in Fig. 8.

When you are certain that you have made all of the connections correctly, turn on the power supply. The far right

LED (LED15) should be turning on and off at the slowest rate while LED14 should be blinking twice as fast, etc. Most of the LEDs will flash too rapidly to detect.

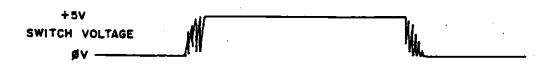

If an oscilloscope is available, use it to observe the output voltage at either terminal A3 or A4. (See Fig. 8 for oscilloscope connections. Be certain to connect the ground of the oscilloscope to one of the GND terminals on the CA-24 board.) The oscilloscope trace should have the appearance something like the idealized diagram shown below. Note, however, that the actual oscilloscope trace probably will have an overshoot spike at the beginning of each high and low level. These overshoot spikes are not detrimental to the function of the clock circuit.

Use a screwdriver to turn the frequency adjust potentiometer, Rll. Observe the change in the oscilloscope pattern. Each pulse width should be within the range of 7 microseconds (highest frequency) to 20 microseconds (lowest frequency).

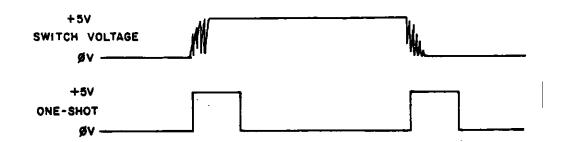

After noting the width of each pulse for a particular setting of R11, connect the oscilloscope to terminal A5, then to A6. The change in trace should be as shown below where each pulse width is twice the previous one.

If an oscilloscope is not available (or after the oscilloscope has been used), the frequency of the clock can be measured by determining the rate at which the far right LED blinks on and off. For example, if that LED (LED15 connected to CLK16) blinks on and off at a rate of 10 blinks in 14.3 seconds (a frequency of 0.70 Hz), then the divide-by-two raised to the sixteenth power or 65536 rate is 0.70 Hz. The original oscillation frequency is 65536 times higher, or about 46000 Hz. Alternatively, multiplying by 65.536 will give the original frequency in kilohertz. By using this method, the maximum and minimum clock frequencies can be measured. Fill in the table below, to confirm the frequency range over which the clock oscillates.

The value for the maximum frequency of the clock will be used in Experiment 12. Furthermore, you may at some later date need the maximum or minimum value as you use the CA-24 board in your own work. Consequently, we recommend that you make a careful measurement and record the values.

| Clock Adjust Resistor<br>(R11) Position | Time for LED 15<br>to Blink if times<br>(T) | Blink Frequency<br>of LED15<br>(F(15)=1\$/T) | Clock Frequency<br>(F(CLK)=F(15)*<br>65.536) |

|-----------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------------|

| Fully Clockwise                         | •                                           | Hz                                           | kHz                                          |

| Fully Counter-Clockwise                 |                                             | Hz                                           | kHz                                          |

Note that upon disconnecting the CIN signal (wire removed from A4), the LED display stops changing and maintains the pattern it had at the instant that the wire was disconnected. When the wire is again connected to A4, the change in pattern resumes without a reset of the LED conditions. If it is desired to reset the LED's, turn off the power supply then turn it back on. Under most applications, continuous signal rates are needed, and the unavailability of a reset signal is not a problem.

This experiment used all 16 divide-by-two circuits connected, in numerical sequence, to the 16 LED's. The layout on the board for doing this is a bit messy. Since, as you observed, most of the LED's blinked too rapidly to count, connection to only the last two or three would have fulfilled the purpose of the experiment. (You probably were aware of this fact as you made the connections.) However, connections to all lights were suggested to emphasize the fact that the glowing of an indicator does not necessarily tell the whole story. What appears to be an "on" condition may be a rapidly varying "on-off" condition.

# EXPERIMENT 4

TITLE

AND Gate

#### **PURPOSE**

The purpose of this experiment is to investigate the function of the AND gate which is used in digital circuits.

# EQUIPMENT

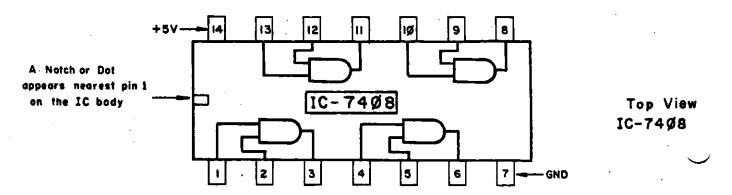

CA-24 board with power supply Five short jumper wires Two medium jumper wires One 7408 IC chip

# DISCUSSION

Logic circuits are the basis for computer operation. Understanding their functions permits the user of an interfaceable computer to perform time critical computer operations in hardware. Since you are now a CA-24 board user, you probably will wish to use a variety of logic circuits, such as the AND gate, the NAND gate, the OR gate, etc. If you are an accomplished user of these logic circuits and their combinations, you may wish to proceed directly to SECTION III where the experiments involving a computer begin.

Perhaps the simplest and certainly a very common logic circuit is the AND gate. The schematic representation is shown below.

The input signals to the AND gate would be on the wires represented by the two lines on the left and the output signal would be on the wire represented by the line on the right.

As has been mentioned earlier, a 5 V signal is called a "true" or logic "1" level. A Ø V signal is called a "false" or logic "0" level. The convention of referring to the more positive voltage level of the two possible levels as "true", is called the "positive" logic convention. We will work only with the "positive" logic convention.

The AND gate functions to produce a logic "1" at the output only when both inputs (input A AND input B) are at logic "1". If either input or both inputs are at logic "0", the output is at logic "0".

There is a standard notation associated with the binary system of logic (or Boolean algebra as it is called in honor of

George Boole, a nineteenth century Englishman) of which the AND gate is our first example. Some of the texts listed in Appendix 3 include detailed discussions of Boolean algegra. The AND operation is symbolized by a dot between the symbols for the input signals. Consequently, the function of the AND gate can be written as:

$output = A \cdot B$

Sometimes the dot is left out in which case the notation becomes:

output = AB

Additional notation will be introduced in the following experiments.

There are four AND gates in the 7408 IC chip which is shown schematically below.

Reference to the diagram will allow determination of input and output pins for the various gates. Pin one is marked on IC chips in one of two ways. On some chips a small dot is placed at one end, off center and near pin one. If used, this is the clearest manner of marking pin one. A notch at one end of the chip (on the center line of the chip) is often used to indicate the end containing pin one (and also the highest numbered pin), see the drawing above. Finally, some manufacturers use both a dot and a notch to mark pin one. Plastic chips may have one or two circular mold marks on the centerline of the chip. Do not confuse these with the "pin one" marks described above.

# PROCEDURE

Many of the experiments in this manual require that you insert IC chips on the CA-24 board. The following instructions describe how to remove IC chips from the board without damaging their pins.

CAUTION - Use extreme care in removing any IC chip from a terminal strip. It is a very common experience to have one end or side of the chip suddenly come free as the chip is being removed. The result is that the pins remaining in the holes are badly bent and

Front

Figure 9

Switch and LED Connections to an AND Gate

Figure 10 Schematic for AND Gate Circuit

may be broken off. A good technique is loosen the chip slightly then insert a small screwdriver or narrow knife blade under the chip and slowly pry up first one end and then the other without ever tilting the chip very much. BE SURE THE POWER IS OFF WHEN YOU DO THIS.

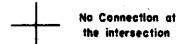

Be certain that the power supply to the CA-24 board turned off. Insert a 7408 IC chip into terminal strip F so that it spans the center groove, is left of center, and has pin 1 to the left (see Fig. 9). The chip can be placed anywhere on the board as long as it spans a center groove of strip B, D, or F. We have chosen the location shown in Fig. 9 because it is close, but not too close, to the LED's which will be used for display of logic levels. Use the two medium length jumper wires to connect pin 14 to terminal G1 and pin 7 to G2. These connections are the 5 V and GND power connections. Next, use four short jumper wires to connect SW1A (terminal G9) and SW2A (terminal GlØ) to LEDØ and LED1 respectively, and to the input of the AND gate associated with pins 1 and 2 of the 7408 chip. The connections are shown on the schematic diagram in Fig. 10, and on the drawing in Fig. 9. Finally use a short jumper wire to connect the output of the AND gate to LED2 as shown in Fig. 9. You will note that on the schematic diagram, a connection is represented by a dot as shown below.

If there is to be no connection when lines cross, then the dot is omitted.

When you are certain that all connections have been made correctly, turn on the power supply. Set switches 1A and 2A to various combinations and observe the three LED's. Remember that when LEDØ is on, one gate input signal (from SW1A) is 5 V or logic "1" while LEDØ off means that the input is Ø V or logic "0". Similar statements hold for LED1 and SW2A. When LED2 is on, the gate output is 5 V or logic "1" while LED2 off means that the gate output is Ø V or logic "0".

The combination of input and output signals can be arranged in an organized fashion called a truth table. Such a table is shown below with the two input columns filled in. Position SWIA and SW2A so that LEDØ and LEDI correspond to the condition shown on each line, then fill in the last column. For example, set SWIA and SW2A so that both LEDØ and LEDI are off (logic "Ø"). Note the condition of LED2 and write Ø or I in the third column depending on whether LED2 is off or on.

| SW 1A             | SW 2A             | OUTPUT            |

|-------------------|-------------------|-------------------|

| (LED Ø condition) | (LED   condition) | (LED 2 condition) |

| Ø                 | Ø                 |                   |

| 1                 | Ø                 |                   |

| Ø                 | 1                 |                   |

| 1                 | 1                 |                   |

The output of the AND gate should be logic "1" only when both inputs are at logic "1". That is, LED2 should be on only when both LEDØ and LED1 are on. If either or both of the input indicators are off, LED2 should be off. In terms of the "true" and "false" designations, the output is "true" only when both inputs are "true". If either input is "false", the output is "false".

Another way of describing the gate function is in terms of signal transmission through the gate. If SW1A is kept in its logic "1" position, then the AND gate output display reports the status of SW2A. If SW1A is kept in its logic "0" position, the output display is off regardless of the position of SW2A. Consequently, it can be said that SW1A enables the gate, permitting the status of SW2A to be transmitted through the gate.

### EXPERIMENT 5

TITLE

NAND Gate and Inverter

#### **PURPOSE**

The purpose of this experiment is to investigate the function of the logic circuit NAND gate and to use it as an inverting element.

#### **EQUIPMENT**

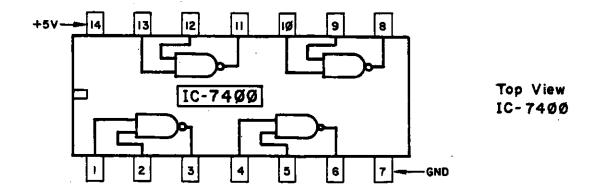

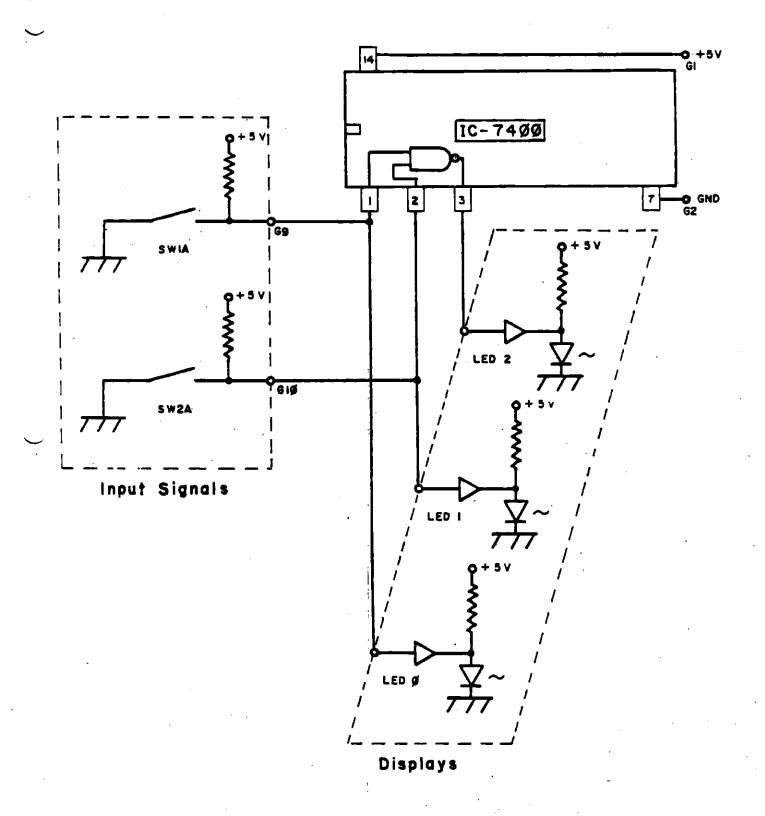

CA-24 board with power supply Five short jumper wires Two medium jumper wires One 7400 IC chip

### **DISCUSSION**

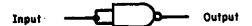

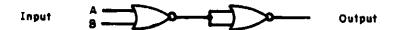

The NAND (NOT AND) gate combines an AND gate and an inversion of the output signal. The schematic representation of the NAND gate is shown below.

Note that the only difference between the AND gate symbol and the NAND gate symbol is the circle at the output of the NAND gate which represents inversion. For the NAND gate, therefore, when both inputs are at logic "1", the output is at logic "0" rather than at logic "1" which would be the case for an AND gate. Any other condition produces a logic "1" at the output.

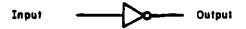

A NAND gate can be used to change a 5 V or logic "1" signal into a Ø V or logic "Ø" signal or vice versa. This is done by connecting together the two inputs so that the same signal appears at both of them. Schematically, a NAND gate used as an inverting element looks like that shown below.

There is a general symbol for an inverting element which differs from the symbol for an identity element (see page 10) in the same way that the NAND gate symbol differs from the AND gate symbol; a circle is added to the output end. Any circuit which inverts, then, can be represented as shown below.

The standard notation which we began to develop in Experiment 4 uses a bar over a symbol or group of symbols to represent inversion. The simple inversion, then, is expressed as

output = input

while the NAND gate function would be written as follows:

output =  $\overline{A \cdot B}$

There are four NAND gates in the  $7400\,$  IC chip which is shown schematically below.

Reference to the diagram will allow determination of input and output pins for the various gates.

#### **PROCEDURE**

Be certain that the power supply to the CA-24 board is turned off. If the circuit of Experiment 4 is still hooked up on the board, simply replace the 7408 chip with a 7400 chip.

CAUTION - Use extreme care in removing the chip. As explained in Experiment 4, it is very easy to damage the pins as the chip is being removed. Use the procedure suggested in the CAUTION note found in that experiment.

The wiring will then be that shown schematically in Fig. 11. If the wiring of Experiment 4 has been changed, replace the jumper wires as described in that experiment and shown in Fig. 12.

When you are certain that all connections have been made correctly, turn on the power supply. Set switches 1A and 2A to various combinations and observe the three LED's. Remembering the convention of LED on being a 5 V signal or logic "1" and the LED off being a Ø V signal or logic "Ø", fill in the truth table at the top of page 32.

Figure 11 Schematic for NAND Gate Circuit

Front

Figure 12

Switch and LED Connections to a NAND Gate

|  | SW 1A             | SW 2A             | OUTPUT            |

|--|-------------------|-------------------|-------------------|

|  | (LED Ø condition) | (LED 1 condition) | (LED 2 condition) |

|  | Ø                 | Ø                 |                   |

|  | 11                | Ø                 |                   |

|  | ø                 | l                 |                   |

|  | 1                 | 1                 |                   |

The output of the NAND gate should be logic "0" only when both inputs are logic "1".

If you wish to observe the NAND gate functioning as an inverter, first turn off the power supply then remove the jumper wire connecting GlØ to LED1. Next, for the wire connecting pin 2 to GlØ, shift the end which is in a GlØ terminal hole to pin 1 of the 7400. The circuit will then be as shown schematically in Fig. 13 and pictorially in Fig. 14. Now turn on the power supply. Note that as SWIA is moved back and forth, LEDØ and LED2 will always be in the display conditions opposite to one another.

Returning the circuit to the NAND gate form will facilitate wiring changes for Experiment 6.

Figure 13

Schematic for a NAND Gate Used as an Inverter

Front

Figure 14

Switch and LED Connections to a NAND Gate Inverter

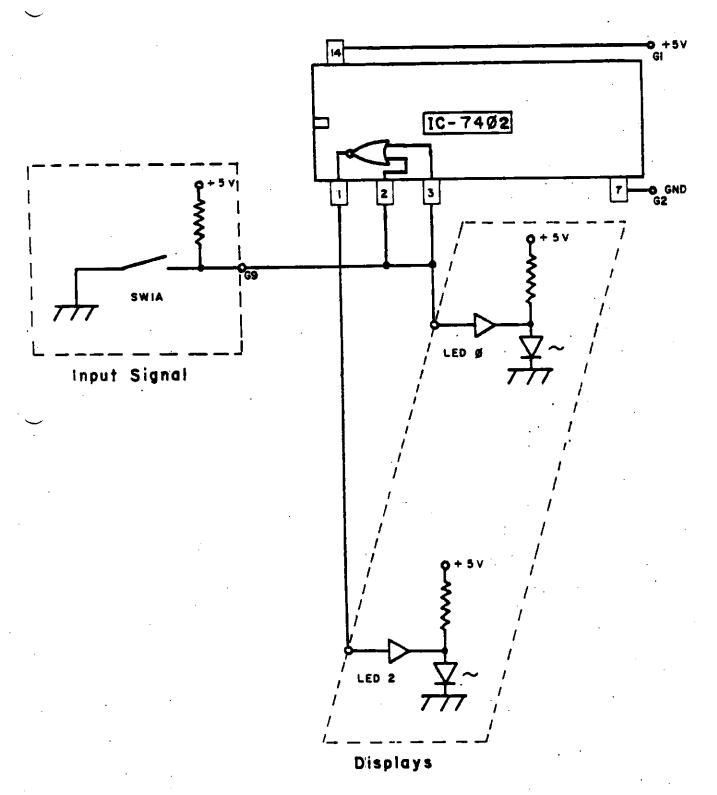

TITLE

NOR Gate and Inverter

#### **PURPOSE**

The purpose of this experiment is to investigate the function of the logic circuit NOR gate and to use it as an inverting element.

## EQUIPMENT

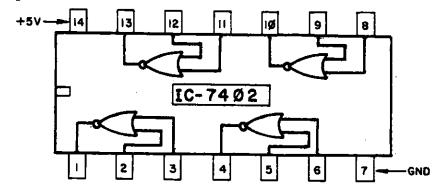

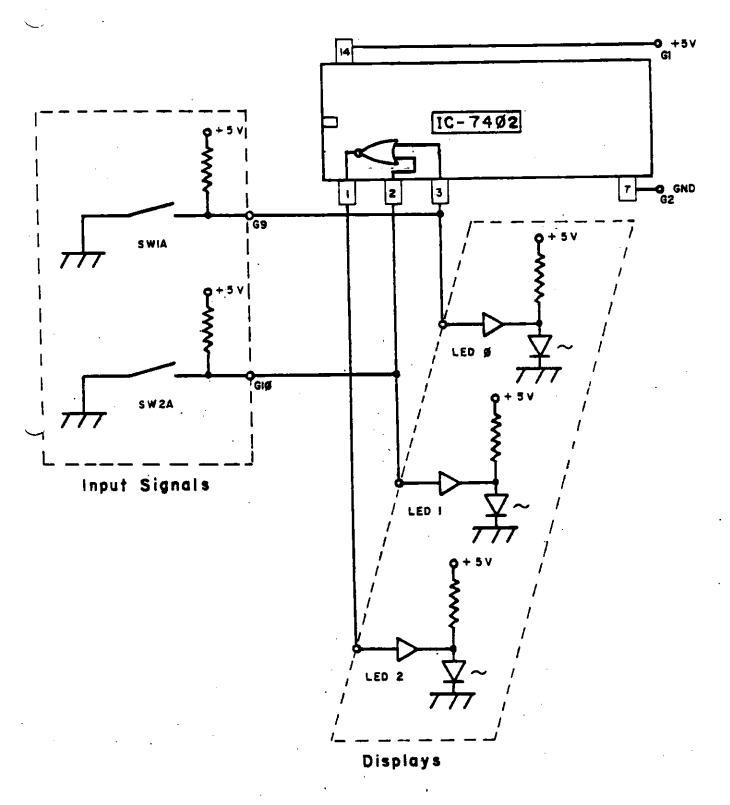

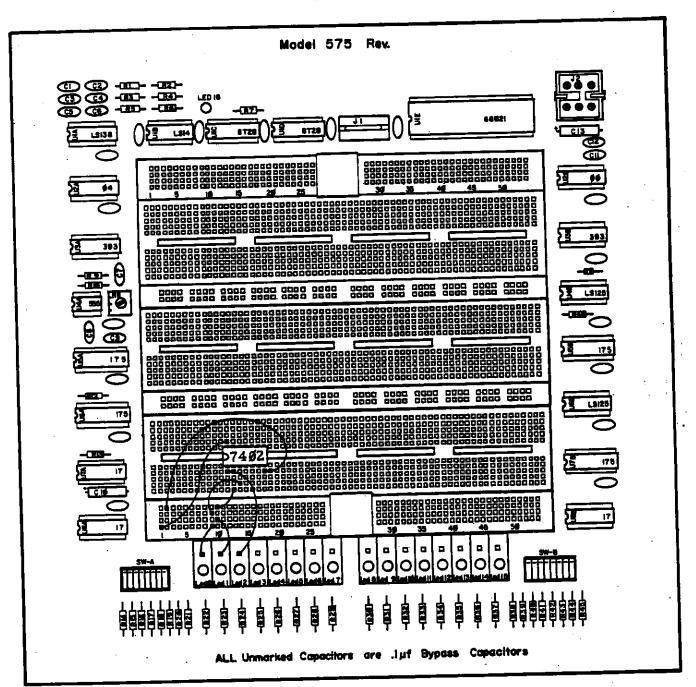

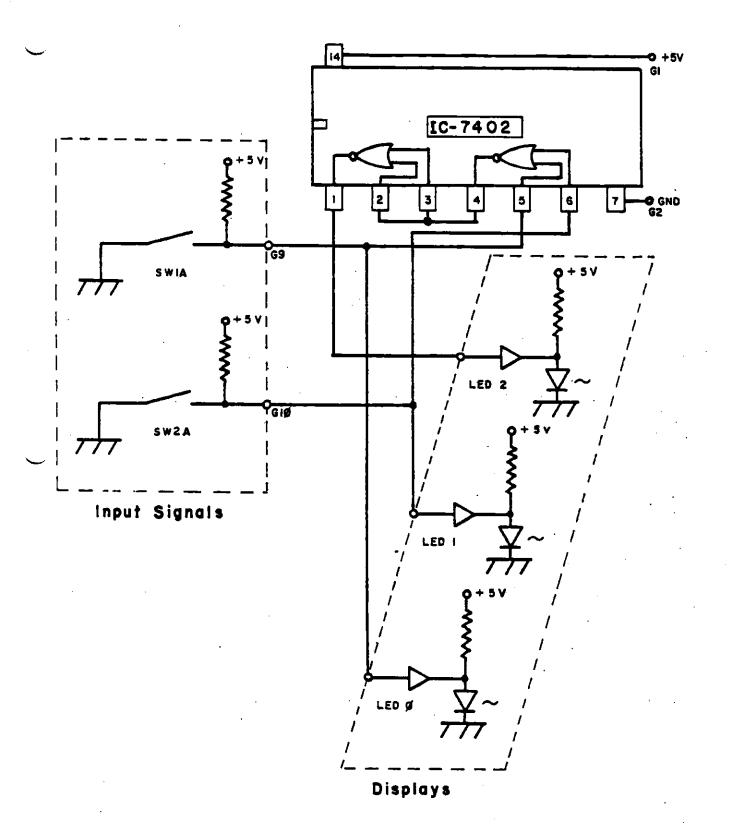

CA-24 board with power supply Five short jumper wires Two medium jumper wires One 7402 IC chip

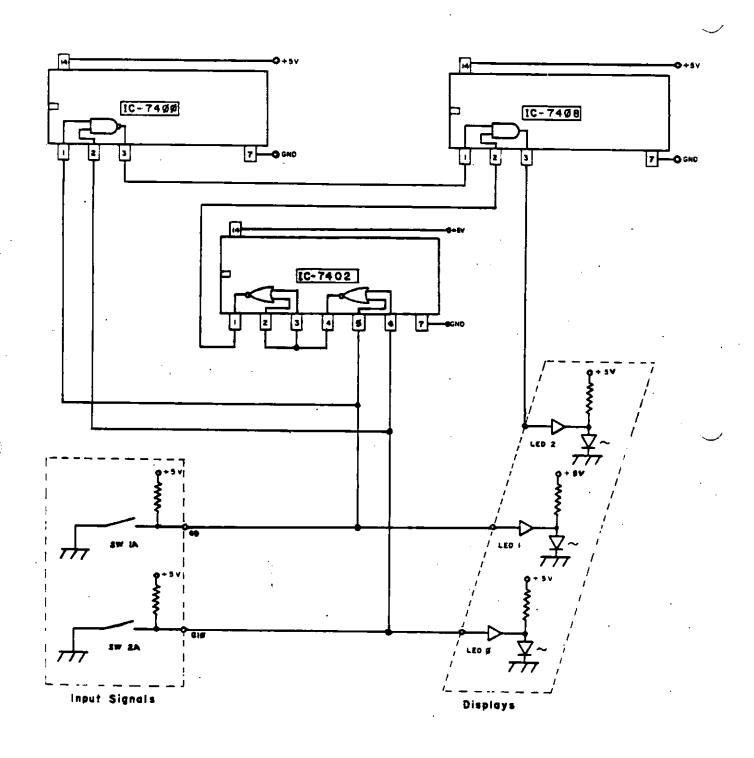

# **DISCUSSION**

The NOR (NOT OR) gate combines an OR gate (which will be investigated in Experiment 7) and an inversion of the output signal. Since NOR gate IC chips are significantly less expensive than OR gate chips and since OR gates can easily be made from NOR gates, we will work with only the NOR gate chip. The schematic representation of the NOR gate is shown below.

The function of the NOR gate is to produce a logic "g" (inverted logic "l") when either one of the inputs is logic "l". The "either/or" function is not, however, exclusive of the "both" condition for the inputs. That is, the output of the gate is also logic "g" when both inputs are high. The only condition which produces a logic "l" at the output is that of both inputs at logic "g".

The standard notation representing a NOR gate function is a combination of the OR operation and an inversion. The + symbol represents the OR operation. Consequently, the NOR gate function is written as follows:

output =

$$\overline{A + B}$$

A NOR gate can be used as an inverting element by connecting together the two inputs so that the same signal must always appear at both of them. The schematic diagram for using the NOR gate as an inverter is shown below.

There are four NOR gates in the 7402 IC chip which is shown in the diagram below.

Reference to the diagram will allow determination of the input and output pins for the various gates.

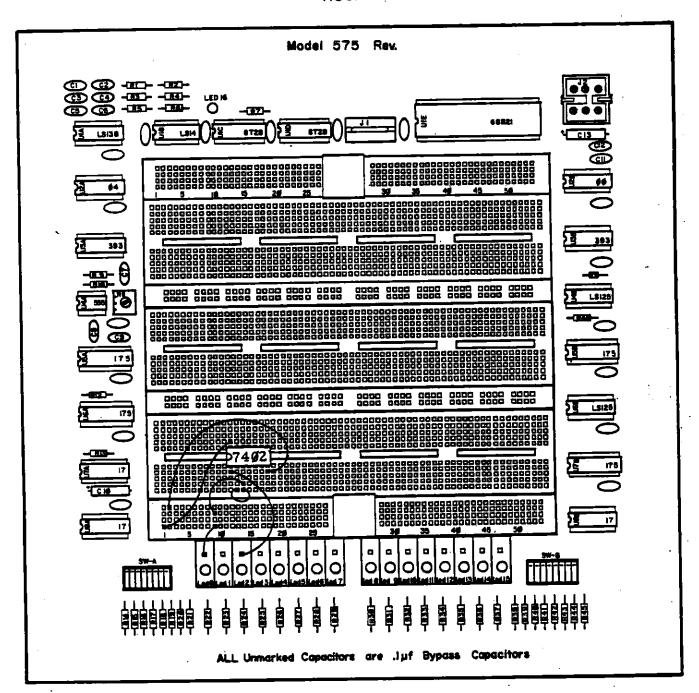

#### PROCEDURE

Be certain that the power supply to the CA-24 board is turned off. If the circuit for Experiment 5 is still on the CA-24 board, remove the 7400 chip and replace it with the 7402 chip. Next, shift jumper wires until the circuit has been connected as shown schematically in Fig. 15 and pictorially in Fig. 16. Note that if the circuit in Experiment 5 was left in the NAND gate form, only two changes are needed. The jumper wire which connected G9 to pin 1 should now connect G9 to pin 3 and the jumper which connected LED2 to pin 3 should now connect LED2 to pin 1.

When you are certain that all connections have been made correctly, turn on the power supply. Set switches 1A and 2A to various combinations and observe the three LED's. Fill in the truth table below.

| SW 1A             | SW 2A             | OUTPUT            |

|-------------------|-------------------|-------------------|

| (LED Ø condition) | (LED   condition) | (LED 2 condition) |

| Ø                 | Ø                 |                   |

| 1                 | Ø                 |                   |

| Ø                 | 1                 | •                 |

| 1                 |                   |                   |

The output of the NOR gate should be logic "1" only when both inputs are logic "g".

If you wish to observe the NOR gate functioning as an inverter, simply remove the jumper wire connecting GlØ to LED1. Then for the wire connecting pin 2 to GlØ, shift the end which is in a GlØ terminal hole to pin 3 of the 7402. The circuit will then be as shown schematically in Fig. 17 and pictorially in Fig. 18. Note that as SWIA is moved back and forth, LEDØ and LED2 will always be in the display conditions opposite to one another.

Returning the circuit to the NOR gate form will facilitate wiring changes for Experiment 7.

Figure 15 Schematic for NOR Gate Circuit

Front

Figure 16

Switch and LED Connections to a NOR Gate

Figure 17

Schematic for a NOR Gate Used as an Inverter

Front

Figure 18

Switch and LED Connections to a NOR Gate Inverter

# EXPERIMENT 7

TITLE

OR Gate from NOR Gates

#### **PURPOSE**

The purpose of this experiment is to construct an OR gate using two NOR gates and to investigate its function.

### EQUIPMENT

CA-24 board with power supply Seven short jumper wires Two medium jumper wires One 7402 IC chip

#### DISCUSSION

The function of an OR gate is to produce a logic "1" signal at the output when either of the two inputs (or both) is at logic "1". The symbol for an OR gate is shown below.

In terms of the standard notation of Boolean algebra, the OR gate function is written as follows:

# output = A + B

Since NOR gates are easier to manufacture than are the OR gates, it is common practice to construct OR gates from NOR gates. This is done simply by sending the output of the NOR gate through an inverter. The combination is shown schematically in the following diagram. The output from the NOR gate is the inverse of A+B. When the output of the NOR gate is sent through an inverter, the result is A+B (that is the inverse of the inverse of A+B is just A+B itself).

## **PROCEDURE**

Be certain that the power supply to the CA-24 board is turned off.  $\,^{\prime}$  If the NOR gate circuit of Experiment 6 is still on

the board, shift the wires which currently connect terminals G9 and G10 to pins 2 and 3, so that they now connect G9 and G10 to pins 5 and 6. Next, use two additional jumper wires to connect together pins 2, 3, and 4. The circuit should then be as shown in the schematic diagram of Fig. 19 and the drawing of Fig. 20.

When you are certain that all connections have been made correctly, turn on the power supply. Set switches 1 and 2 to various combinations and observe the three LED's. Fill in the truth table below.

| SW 1A             | SW 2A             | OUTPUT            |

|-------------------|-------------------|-------------------|

| (LED Ø condition) | (LED 1 condition) | (LED 2 condition) |

| Ø                 | Ø                 |                   |

| 1                 | Ø                 |                   |

| Ø                 | l                 |                   |

| 1                 | 1                 |                   |

The output of the OR gate should be logic "0" only when both inputs are logic "0".

Figure 19 Schematic for an OR Gate Made From NOR Gates

Front

Figure 20 Switch and LED Connection to OR Gate

### EXPERIMENT 8

TITLE

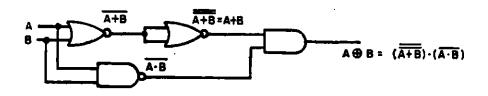

Exclusive OR Gate from AND, NAND, and NOR Gates

### **PURPOSE**

The purpose of this experiment is to construct an exclusive OR gate using the three gates which were studied in Experiments 4, 5, and 6 and to investigate its functions.

# EQUIPMENT

CA-24 board with power supply Eight short jumper wires Eleven medium jumper wires One 7400 IC chip (NAND gates) One 7402 IC chip (NOR gates) One 7408 IC chip (AND gates)

#### DISCUSSION

The function of an exclusive OR gate is to produce a logic "1" signal at the output when either of the two inputs is at logic "1", but not when both are at logic "1". For the exclusive OR gate, then, both inputs at logic "0" or at logic "1" will produce an output of logic "0".

The symbol for the exclusive OR gate is shown below.

In the standard notation of Boolean algebra, the exclusive OR operation is represented by the symbol . The function of the exclusive OR gate, then, would be written as follows:

## output = A ⊕ B

It is possible to purchase an IC chip which has exclusive OR gates in it (the 7486). However, if AND, NAND, and NOR gates are already being used, it is frequently advantageous to construct the exclusive OR from the others. The diagram for doing this is shown below.

Note that the Boolean algebra notation has been included to show how equations could be used instead of diagrams to represent the circuit functions.

#### PROCEDURE

Be certain that the power supply to the CA-24 board is turned off. Remove any chips and wires left on the board from previous work and then position the three IC chips as shown in Fig. 21. Make all the necessary connections using the short and medium jumper wires where appropriate. It probably will be helpful to refer to the schematic diagram in Fig. 22 as well as the pictorial representation while inserting the jumper wires. Note that strip E is being used as a power distribution strip. This procedure helps to keep the board organized.

When you are certain that all connections have been made correctly, turn on the power supply. Set switches 1A and 2A to various combinations and observe the three LED's. Fill in the truth table below.

| SW 1A             | SW 2A             | OUTPUT            |

|-------------------|-------------------|-------------------|

| (LED Ø condition) | (LED   condition) | (LED 2 condition) |

| Ø                 | Ø                 |                   |

| 1                 | Ø                 |                   |

| Ø                 | 1                 |                   |

| 1                 | 1                 |                   |

The output (LED2) of this exclusive OR gate should be logic "0" (off) when both inputs (LED's  $\emptyset$  and 1) are at logic "0" (off) or at logic "1" (on). The output should be at logic "1" when either input is at logic "1".

Front

Figure 21 Switch, LED, and Inter-Chip Connections for an Exclusive OR Gate

Figure 22 Schematic for an Exclusive OR Gate Made From AND, NAND, and NOR Gates

TITLE

The R-S Flip-Flop (RSFF)

#### PURPOSE

The purpose of this experiment is to become familiar with the basic digital flip-flop circuit and to construct and test an R-S (Reset-Set) flip-flop with an enable-disable input.

### EOUIPMENT

CA-24 board with power supply Eleven short jumper wires Five medium jumper wires One 7400 IC chip

### DISCUSSION

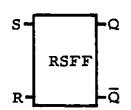

The flip-flop circuit is one for which the output has two stable conditions which can be changed from one to the other by a proper combination of signals at the input. A simple flip-flop is the R-S flip-flop. The "black box" representation of this device is shown below together with its truth table.

| S | R | Q          | ΩΙ |

|---|---|------------|----|

| Ø | Ø | No Change  |    |

| 1 | Ø | 1          | Ø  |

| Ø | 1 | Ø          | 1  |

| 1 | 1 | Indefinite |    |

It is common practice to label the two output signals Q and  $\overline{Q}$  where  $\overline{Q}$  always has the opposite value from Q. This flip-flop is not used with the condition of both R and S being at logic "1".

The flip-flop circuit in this experiment can be compared to a fluorescent desk lamp (Q) controlled by two push button switches (R and S). Push button S (the set switch) is used to turn the lamp on. Once the lamp is on, pressing S has no further effect until the lamp is turned off again. Push button R (the reset switch) is used to turn the lamp off. Once the lamp is off, pressing R has no further effect until the lamp is turned on again. Pressing both buttons simultaneously yields indefinite results. As you read through the following discussion, it may help to identify the terminology low and logic "B" with "off" and high and logic "l" with "on".

The terms set and reset come from the condition that, from the starting condition of both inputs at logic "0", the set signal going high will set Q to logic "1" and the reset signal going high will reset Q to logic "0". With R low, then, S going high will produce at Q a high which will stay there when S is made low again. This is one of the two stable conditions. As

long as R is low, changing S back and forth between high and low will not alter the logic "1" at Q. (The "No Change" notation in the truth table means Q stays high when S is made low.) When S is low, however, changing R to high will change Q to low, the second stable condition. As long as S remains low, changing R will not alter the logic "g" at Q. (The "No Change" notation means also that Q stays low when R is made low.)

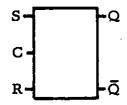

Because the flip-flop has the capability of holding a signal at its output while certain changes are occuring at its input, the flip-flop is sometimes referred to as a latch. The latching feature is enhanced if an additional signal can enable or disable the entire flip-flop. The general diagram for a flip-flop with this capability is shown below.

If the signal at C (for control or clock) is low (logic "g"), the circuit will be disabled, holding whatever condition is at Q. If the signal at C is high (logic "1"), the circuit will function normally. Furthermore, the signal at C can be used to change the condition at Q. If the flip-flop has been reset (level at Q is logic "g") and the signal at C has been put at logic "g", then a high input at S will have no effect. However, if the signal on C is raised to +5 V while the logic "l" is on S, the signal at Q will become logic "l". In this function mode, the flip-flop can be used to transfer a logic "l" signal from S to Q and then hold it at Q.

The two flip-flop circuits described above can be constructed from NAND gates. The circuit diagrams are shown in Figs. 23a and 23b. (Pin numbers for the 7400 IC chip and other CA-24 board designations are also shown there as this figure will be referenced again in the PROCEDURE portion of this experiment.) If you wish to trace the logic level conditions in order to understand why the circuit behaves as it does, it will probably be helpful to begin with a logic "1" at S, a logic "0" at R, and a logic "1" at Q. Q, of course, will be low because the NAND gate for which it is the output has both inputs high. Convince yourself that no change at Q will occur if S is switched low, then with S low, trace through what will happen when R is raised.

## PROCEDURE

Be certain that the power supply to the CA-24 board is off. Remove any chips and wires left on the board from previous work and then position a 7400 IC chip as shown in Fig. 24. Make all the necessary connections using the short and medium jumper wires where appropriate. It probably will be helpful to refer to the schematic diagram in Fig. 23a as well as the pictorial

Figure 23a Schematic for an R-S Flip-Flop Made From NAND Gates

Figure 23b Schematic for an R-S Flip-Flop with Clock Input

Front

Figure 24

Switch, LED, and other Connections for an R-S Flip-Flop

representation while inserting the jumper wires. Note that power connections do not show on the schematic diagram. Be certain that you have G1 connected to pin 14 and G2 connected to pin 7.

When you are certain that all connections have been made correctly, set switches 1A and 3A to the logic "0" position (number end down) and turn on the power supply. Move switch 1A back and forth while noting the condition of LED6 and LED7. With switch 1A in the logic "0" position, move switch 3A back and forth while noting LED6 and LED7. Now go back to changing SW1A (with SW3A left at logic "0"). Finally, remembering that SW1A corresponds to S, SW3A corresponds to R, LED7 corresponds to Q and LED6 corresponds to  $\overline{Q}$ , verify the truth table on page 49. (It will not harm the circuit to have both inputs at logic "1". This condition, however, has no meaning in the functioning of the flip-flop.)

The next step is to add the control or clock feature. As can be seen from figures 23b and 25, this is quite simple to do. First, turn off the power supply and remove the wires connecting pin 12 to 13 and 1 to 2. Then use one of the wires to connect pin 13 to pin 1 and the other wire to connect the combination to terminal G10. Finally, use an additional jumper wire to connect G10 to LED1. The result should be as shown schematically in Fig. 23b and pictorially in Fig. 25.

When the change has been made correctly, turn on the power supply. Use the following procedure to verify the enable and disable function of the signal at C. After setting switch 2A to its low condition, change the levels produced by SW1A AND SW3A and note that the signals at Q and  $\bar{Q}$  do not change. (The flip-flop is disabled.) Set switch 2A to its high condition and note that now the flip-flop functions normally. Use the signal at C as a data transfer signal by resetting the flip-flop, disabling it, setting SW1A to logic "1", then moving SW2A to its logic "1" position.

The clock on the CA-24 board can be used to produce a continuous set of alternating enable-disable signals. Turn off the power supply, then remove the jumper wires which are connecting pin 1 to G1Ø and G1Ø to LED1. Use one of these to connect A3 to A4 (the clock output to the divide chain). Use the other to connect pin 1 directly to LED1. The last connection needs a short wire to connect pin 1 to G26 (the end of the divide chain). The circuit should look like that shown in Fig. 26.

When the changes have been made, turn on the power supply. LED1 should be blinking on and off. Use a screwdriver to adjust the clock frequency until the slowest blink rate is achieved.

Move switches 1A and 3A back and forth at various times during the clock cycle and observe the function of the signal at C. Note that with the flip-flop reset, a logic "1" placed at the S input (LEDØ on) when C is low (LED1 off) will not appear at Q (LED7) until C goes high. However, with the flip-flop

reset, a logic "1" placed at S when C is high will immediately transfer to Q. This uncertainty as to whether the data will transfer immediately or at the beginning of the next clock cycle can be a problem. More sophisticated latch circuits remove this uncertainty. Such a latch circuit will be investigated in Experiment 11.

# Front

Figure 25

Switch, LED, and other Connections for an R-S Flip-Flop with Clock Input

Front

Figure 26

Connection for Use of the On-Board Clock with the R-S Flip-Flop

TITLE

The D Flip-Flop (74175)

### **PURPOSE**

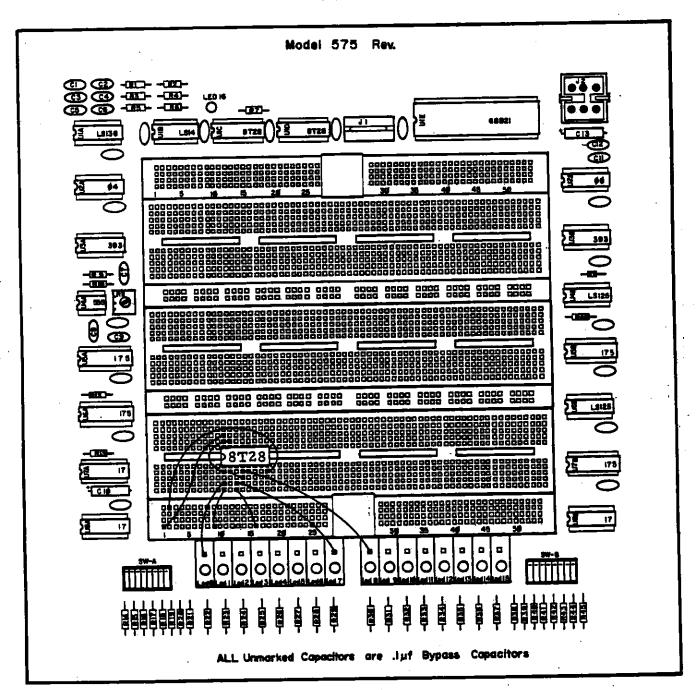

The purpose of this experiment is to investigate the function of a D (delay) flip-flop using a flip-flop on the 74175 IC chip as an example.

# EQUIPMENT

CA-24 board with power supply Six short jumper wires Five medium jumper wires One 74175 IC chip

### **DISCUSSION**

In Experiment 9 it was shown how a flip-flop circuit can transfer a logic level from an input line to an output line and hold (or latch) it there. It was noted that for the relatively simple flip-flop being studied, the logic "1" would be transferred if it appeared at S when the signal at C was high or else the transfer would wait until the signal C went high. A review of that experiment will show that it is only the logic "1" at S which can be transferred by the signal at C (unless the reset signal is changed to logic "1").

The D (delay) flip-flop (DFF) is a more complex circuit which will transfer either level of a data line when the C signal (from now on called clock signal) goes from low to high regardless of when in the clock cycle the data signal appears at the input (from now on referred to as the D input). Note that the transfer is always delayed until the next rise of the clock signal.

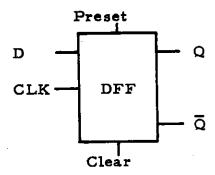

The general diagram for a flip-flop is shown below.

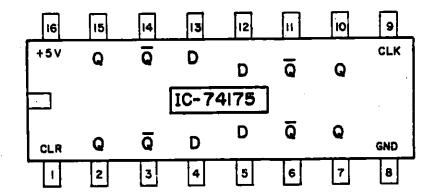

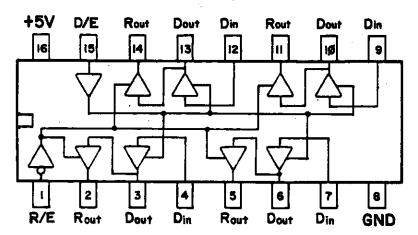

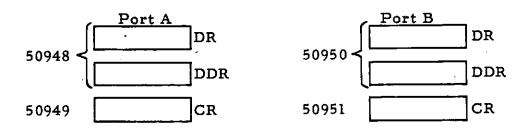

The normal transfer function occurs when both the preset and clear signals are high. If the clear signal is set low, Q is low regardless of the conditions at D and CLK. If preset is low (clear high), then Q is high regardless of the conditions at D The CA-24 board contains four 74175 IC chips, each of which contains four D flip-flops or latches. In experiments and 14 we shall examine the role these chips play in the process when the CA-24 board is interfaced with the computer. In this experiment the extra 74175 IC chip provided with manual is used to study the operation of a D flip-flop. circuits in the 74175 chip are not completely independent but have a common clock line and a common clear line. A further modification is the elimination of the preset input, which is not needed for many applications. The following diagram shows which pins of the 74175 correspond to which signals for the flip-flops. Each set of Q,  $\overline{Q}$ , and D pins corresponds to one of the latches.

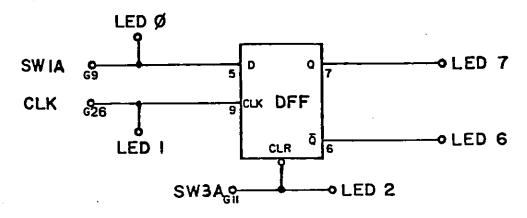

### **PROCEDURE**

Be certain that the power supply to the CA-24 board is off. Remove any chips and wires left on the board from previous work. Insert the extra 74175 IC chip provided with this manual as shown in Fig. 27. The schematic diagram below shows how one of the latches in the chip is to be connected. Not shown on the diagram is the connection of terminal A3 to A4 which connects the clock to the divide chain and, or course, the power connections to the chip. Note that this chip has 16 pins, rather than 14 like the chips used in the previous experiments.

Front

Figure 27

Switch and LED Connections to a D Slip-Flop

Use the various lengths of jumper wires where appropriate to make the connections. Fig. 27 shows how the wires should be positioned.

When you are certain that all connections have been made correctly, turn on the power supply. LED1 should begin blinking on and off.

Move switch 3 to its logic "1" or high position. The status of this switch will show on LED2 which should now be glowing. Move switch 1 from low to high and from high to low at various times during the clock cycle and note the behavior of LED7 (the indicator for Q) and LED6 (the indicator for  $\overline{Q}$ ). Your observation should verify that the data signal (setting of SWIA) is transferred to Q only when the clock signal rises (i.e., only when LED1 turns on).

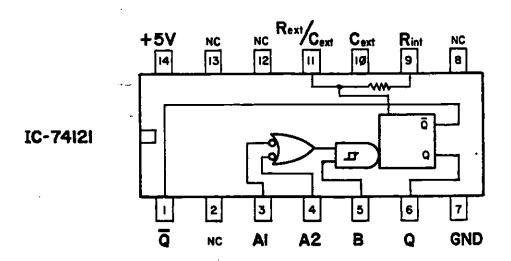

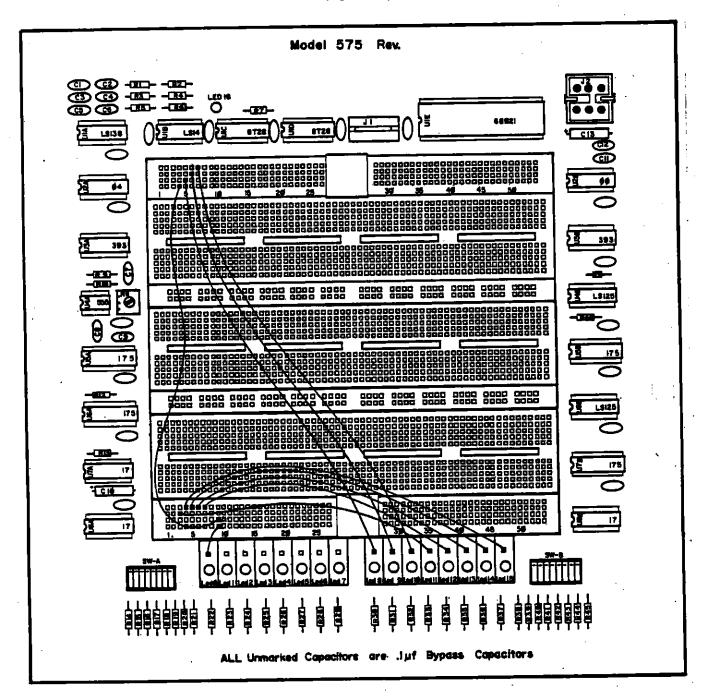

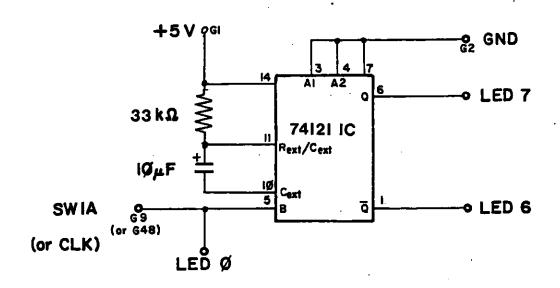

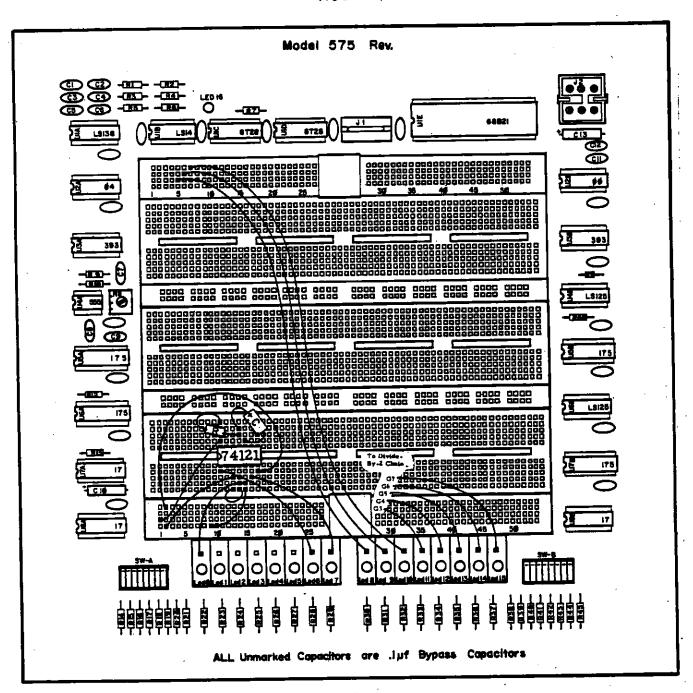

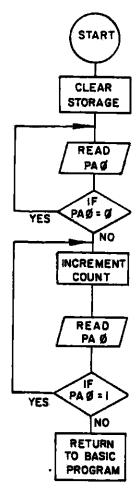

Set SWIA to its logic "1" condition. Move SW3A to its low position at any time during the clock cycle. Note that LED7 will turn off immediately. The clear (logic "0") signal will set Q to logic "0" as soon as it is applied regardless of when in the clock cycle it arrives.